# Customer Advisory ADV2413

Minor Change to the Barcode Labels of Products in the Agilex™ FPGA Portfolio and Stratix® 10 FPGAs & SoC FPGAs

Issue Date: 2024-10-04

## **Description**

Altera is notifying customers on a minor barcode label content change affecting all devices in the Agilex™ FPGA Portfolio and Stratix® 10 FPGAs and SoC FPGAs

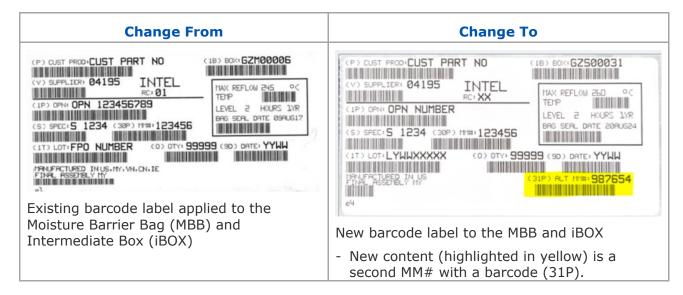

Additional content will be shown on the lower right of the barcode labels applied to the Moisture Barrier Bag (MBB) and the intermediate box (iBOX).

This new content is for a second "MM#, designated as (31P), to be used solely for Altera internal product identification. All other label fields remain the same.

See Table 1 for the details and comparison to the existing label.

Table 1

#### **Recommended Actions**

Customers are requested to review and take note of the change.

This is only a label change and there is no change to the actual products.

There is no impact to form, fit, function, quality and reliability.

#### **Products Affected**

All devices in the Agilex FPGA Portfolio and Stratix 10 FPGAs and SoC FGPAs.

The list of affected part numbers (OPNs) can be downloaded in Excel form from this link: https://cdrdv2.intel.com/v1/dl/getContent/827335

## **Change Implementation**

| Milestone                                                                                                                                                                   | Date             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Earliest shipment using the modified barcode label                                                                                                                          | December 1, 2024 |

| Note: From this date, you may expect to see shipments using either or both previous and the modified barcode labels, until products using the previous labels are depleted. |                  |

### **Reason for Change**

The addition of a second MM# is solely for Altera internal product identification and transaction purposes.

#### **Contact**

For more information, please contact your local Sales representative, or submit a question or request at the My Intel support page, log in via: https://www.intel.com/content/www/us/en/mv-intel/fpga-sign-in.html

# **Customer Notifications Subscription**

If you want to receive customer notifications by email, please follow the instructions in ADV 2209.

Altera references J-STD-046 guidelines for PCN.

In accordance with J-STD-046, this change is deemed acceptable to the customer if no acknowledgment is received within 30 days from the date of notification.

# **Document Revision History**

| Date       | Version | Description     |

|------------|---------|-----------------|

| 2024-10-04 | 1       | Initial release |

<sup>©</sup> Altera Corporation. Altera, the Altera logo, the `a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.