# **Product Change Notification**

#### PCN No: MSS-23-0223-CCB-1112 / MSS-23-1106-CCB-1330

Si55xx/540x New Mold Compound Material and Leadframe surface treatment qualification Si55xx/540x Datasheet Changes and Updates

Notification Date: 11/10/2023 Qualification Data Availability Date: 07/26/2024

Sample Availability Date: 11/10/2023

Proposed First Ship Date for Change: 02/08/2024 Last Date of Manufacture of Unchanged Product: 02/08/2024

Dear Valued Skyworks Customer:

Notification Period: 90 days

Please be advised that Skyworks Solutions Inc. is introducing the following product change(s):

#### **Description and Scope of Change**

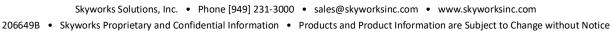

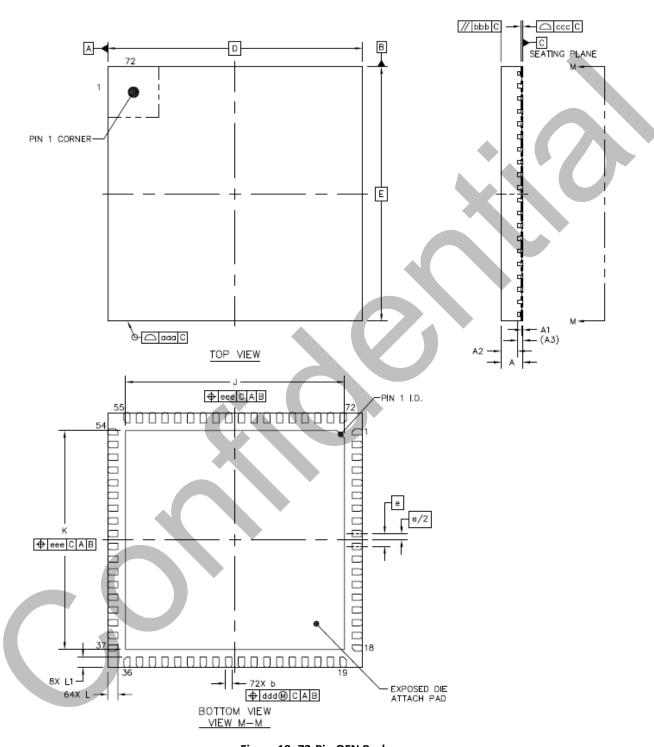

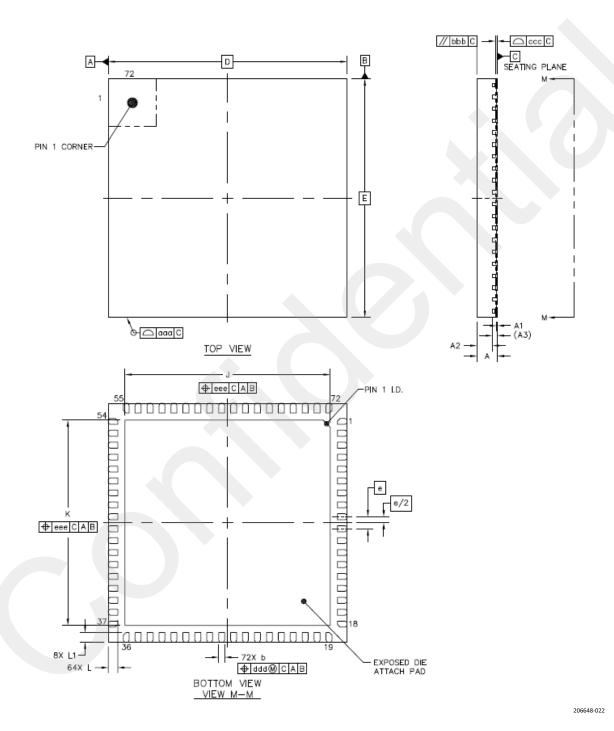

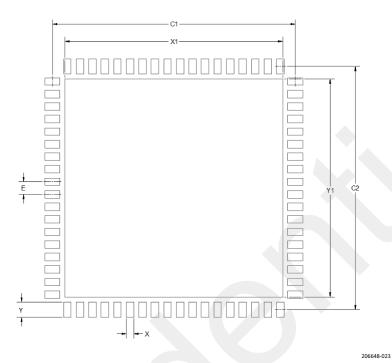

Skyworks has qualified Sumitomo A631HT-G mold compound at ASE Chung Li for QFN products requiring a high thermal conductivity bill of materials. Leadframe will change to a roughened copper version. No dimensional or plating changes. Si55xx/540x products assembled in QFN 10x10 mm package will migrate to the new bill of materials.

Datasheet changes are outlined in the revision blocks of the respective documents. Affected Datasheets:

- Si5510/08 Low-Phase-Noise, Jitter-Attenuating Clock for 5G/eCPRI

- Si5512: NetSync™ Low-Phase-Noise, Jitter-Attenuating Clock for 5G/eCPRI/SyncE/IEEE 1588

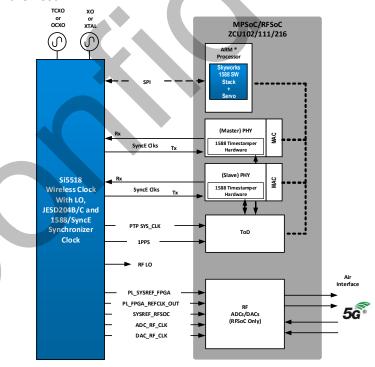

- Si5518 NetSync™ Low-Phase-Noise Jitter-Attenuating Clock for 5G/eCPRI/SyncE/IEEE 1588

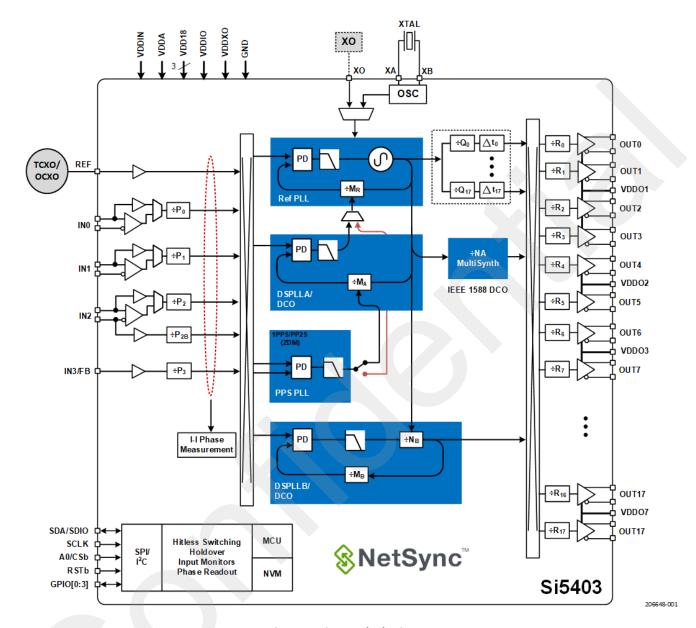

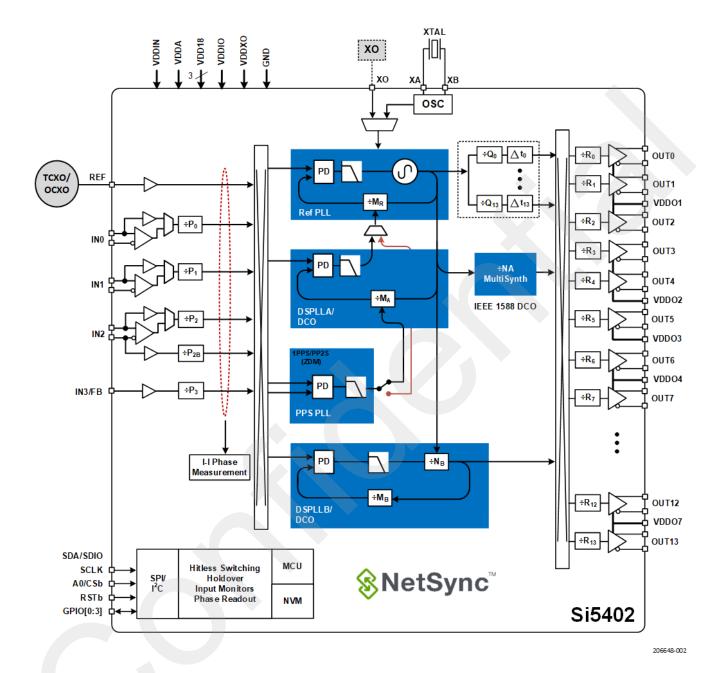

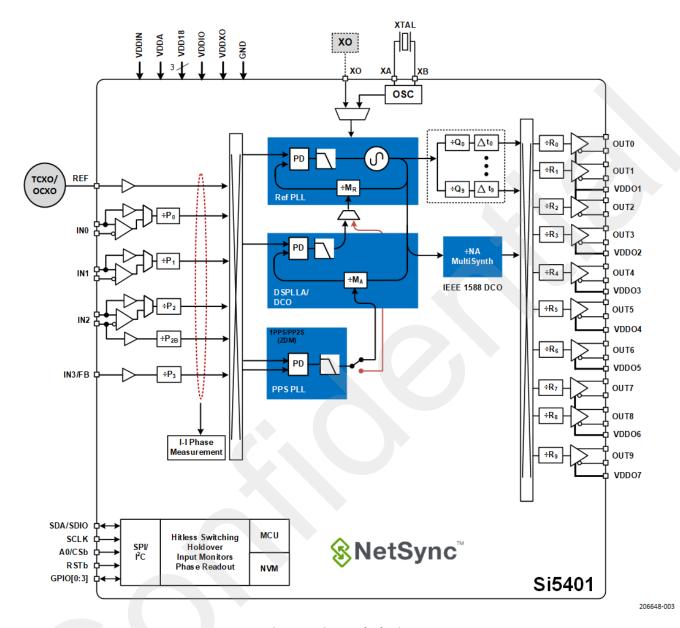

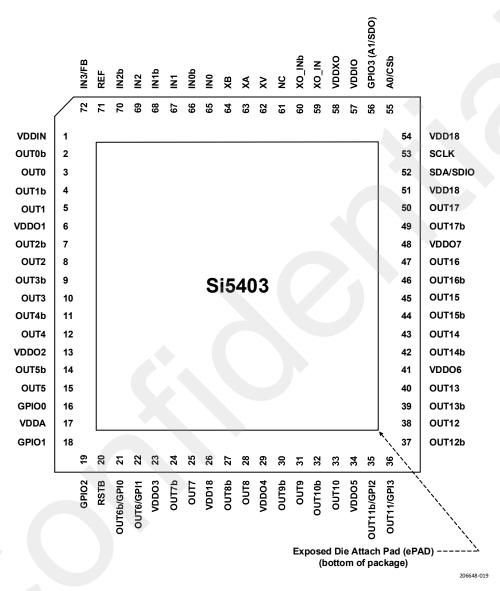

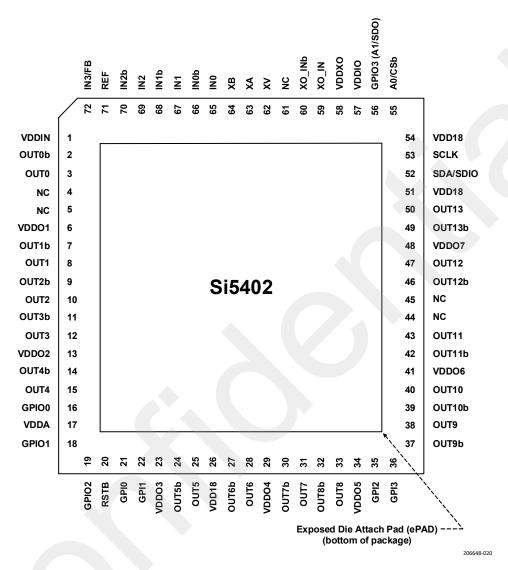

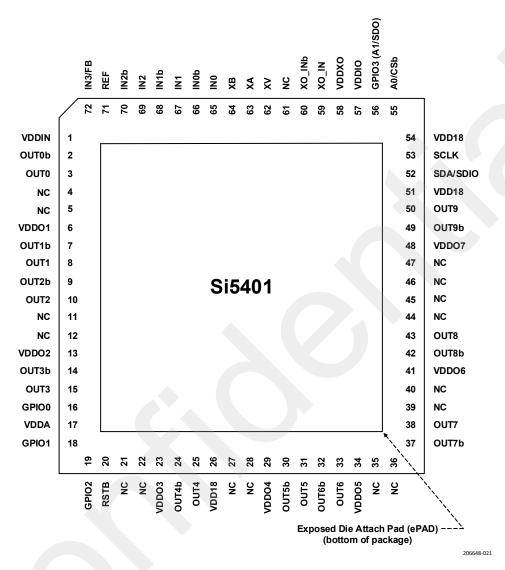

- Si5403, Si5402, and Si5401: NetSync™ Network Synchronizer Clock for 5G, SyncE, and IEEE 1588 Applications

Datasheets attached to PCN letter

#### **Products Affected**

Affected parts defined in the Ordering Guide section of each Datasheet. For the purpose of the PCN letter, these have been consolidated as an addendum.

### Method for Identifying Changed Product

Full product change traceability is maintained by: date code

#### Reason for Change

ASECL is standardizing on Sumitomo A631HT-G for high thermal conductivity mold compound in QFN production.

- . Sumitomo is a leading supplier of mold compound for our OSAT base

- Multiple customers are qualifying this material at ASECL

- Material change enhances assurance of supply and lot-to-lot material consistency.

Si55xx/540x datasheet updates encompass content expansions, template modifications, and typo corrections.

#### Anticipated Impact on Form, Fit Function, Reliability, Durability, Quality or Safety

Impacting form due to mold compound change; no impact to fit, function, realiability, durability, quality or safety.

#### **Qualification Plan Summary**

Required package qualification plan has been successfully completed.

#### Launch Plan

Changes will be implemented at the completion of the PCN effectivity date and upon consumption of existing inventory. Datasheets will be updated in advance of the PCN to allow for customer review of the changes

Please contact your Skyworks customer service representative with any questions or comments regarding this change. If you are unsure whom to contact, please email Skyworks Change Management at Skyworks.CCB@Skyworksinc.com.

#### Skyworks Solutions, Inc.

20 Sylvan Road, Woburn, MA 01801 USA: (781) 376-3000 • Asia: 886 2 2735 0399 Europe: 33 (0)1 43548540 • Fax: (781) 376-3300

On the Web: www.skyworksinc.com

# **Ordering Guides - For Reference**

- Si5510/08

- Si5512

- Si5518

- Si5403, Si5402, and Si5401

# 2. Ordering Guide

Table 1. Si5510/08 Ordering Guide

| Ordering Part Number (OPN) <sup>1, 2, 3</sup> | Number of DSPLLs,<br>MultiSynths | Number of<br>Outputs | Serial Interface        | Package                | Temperature Range                                        |

|-----------------------------------------------|----------------------------------|----------------------|-------------------------|------------------------|----------------------------------------------------------|

| Si5510A-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | −40 to 95 °C ambient<br>−40 to 105 °C board <sup>5</sup> |

| Si5510C-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | 12C                     | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5510D-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | 12C                     | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5510E-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5508A-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>No-MultiSynths        | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5508C-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>No-MultiSynths        | 18                   | 12C                     | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5508D-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>No-MultiSynths        | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si55xx-A-EVB <sup>6</sup>                     | _                                | 18                   |                         | Evaluation board       | _                                                        |

- 1. Add an "R" at the end of the OPN to denote tape and reel ordering options.

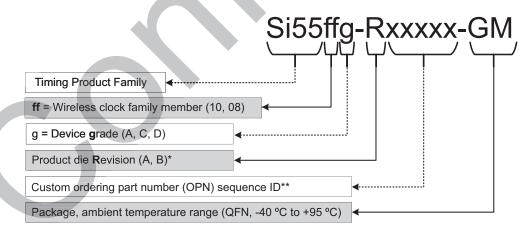

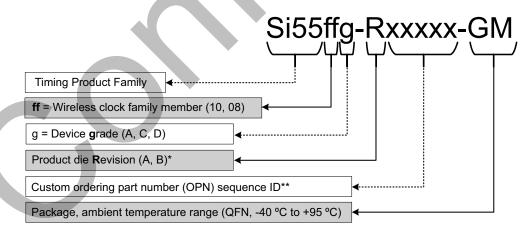

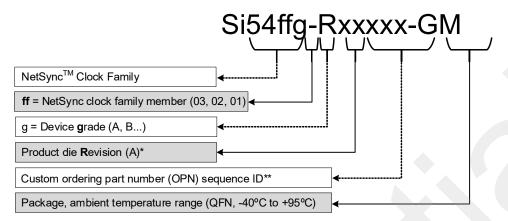

- 2. Custom, factory preprogrammed devices are available. See the figure below for 5-digit numerical sequence nomenclature.

- 3. Revision B will be the device qualified for mass production and loose samples.

- 4. Grade D and E are reserved for special applications, see CBPro for details.

- 5. Si55xx EVB can be configured as either Si5510 or Si5508.

- 6. Si55xx-A-EVB can be configured as either Si5510 or Si5508.

<sup>\*</sup> See Ordering Guide table for current product revision.

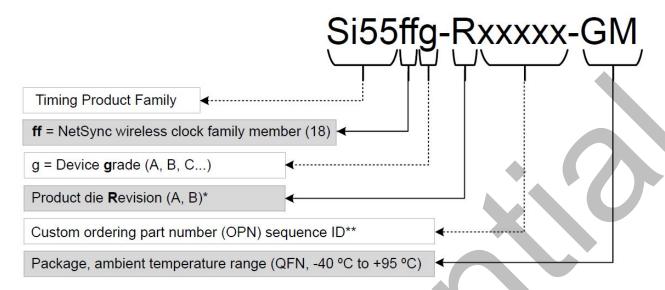

Figure 2. Si5510/08 Ordering Guide Diagram

<sup>\*\* 5</sup> digits; assigned by ClockBuilder Pro for Custom OPN devices.

DATA SHEET Si5512

# 2. Ordering Guide

Table 1. Si5512 Ordering Guide

| Ordering Part Number (OPN) <sup>1,2,3</sup> | Number of DSPLLs    | Number of<br>Outputs | Serial Interface     | AccuTime IEEE<br>1588 Software<br>Support <sup>4</sup> | Package                              | Temperature Range                 |

|---------------------------------------------|---------------------|----------------------|----------------------|--------------------------------------------------------|--------------------------------------|-----------------------------------|

| Si5512A-Bxxxxx-GM                           | 1-RFPLL,<br>2-DSPLL | 12                   | SPI 4–wire or 3–wire | No                                                     | 72-Lead QFN<br>10 x 10 mm            | –40 to 95 °C Ambient <sup>5</sup> |

| Si5512B-Bxxxxx-GM                           | 1-RFPLL,<br>2-DSPLL | 12                   | SPI 4-wire only      | Yes                                                    | 72-Lead QFN<br>10 x 10 mm            | -40 to 95 °C Ambient <sup>5</sup> |

| Si5512C-Bxxxxx-GM                           | 1-RFPLL,<br>2-DSPLL | 12                   | I <sup>2</sup> C     | No                                                     | 72-Lead QFN<br>10 x 10 mm            | –40 to 95 °C Ambient <sup>5</sup> |

| Si5512D-Bxxxxx-GM <sup>6</sup>              | 1-RFPLL,<br>2-DSPLL | 12                   | SPI 4-wire only      | Yes                                                    | <b>72-Lead</b> QFN 10 x <b>10</b> mm | –40 to 95 °C Ambient <sup>5</sup> |

| Si5512E-Bxxxxx-GM <sup>6</sup>              | 1-RFPLL,<br>2-DSPLL | 12                   | SPI 4-wire only      | Yes                                                    | 72-Lead QFN<br>10 x 10 mm            | -40 to 95 °C Ambient <sup>5</sup> |

| Si5512P-Bxxxxx-GM <sup>6</sup>              | 1-RFPLL,<br>2-DSPLL | 12                   | SPI 4–wire or 3–wire | No                                                     | 72-Lead QFN<br>10 x 10 mm            | –40 to 95 °C Ambient <sup>5</sup> |

| Si5512Q-Bxxxxx-GM <sup>6</sup>              | 1-RFPLL,<br>2-DSPLL | 12                   | SPI 4–wire or 3–wire | Yes                                                    | 72-Lead QFN<br>10 x 10 mm            | –40 to 95 °C Ambient <sup>5</sup> |

| Si5512R-Bxxxxx-GM <sup>6</sup>              | 1-RFPLL,<br>2-DSPLL | 12                   | I <sup>2</sup> C     | No                                                     | 72-Lead QFN<br>10 x 10 mm            | –40 to 95 °C Ambient <sup>5</sup> |

| Si55xx-A-EVB                                | 1-RFPLL,<br>2-DSPLL | 12                   | _                    | No                                                     | Evaluation Board                     | _                                 |

| Si5518-A-FMC-EVB <sup>7</sup>               | _                   | _                    | -                    | Yes                                                    | FPGA Mezzanine<br>Card (FMC)         | _                                 |

- 1. Add an "R" at the end of the OPN to denote tape and reel ordering options.

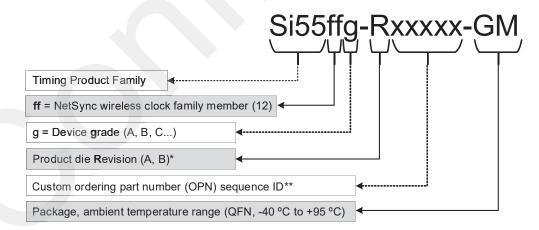

- 2. Custom, factory preprogrammed devices are available as well as unconfigured base devices. See Figure 1 for 5-digit numerical sequence nomenclature.

- 3. Revision B will be the device qualified for mass production and loose samples.

- 4. AccuTime IEEE 1588 software is only supported on certain part grades. Use this table to determine which grades support AccuTime.

- 5. Ambient temperature of 95 °C may not be possible with all configurations. This is dependent on device configuration. Tj cannot exceed a max of 125 °C.

- 6. Grades D, E, P, Q, and R are reserved for special applications. See ClockBuilder Pro for details.

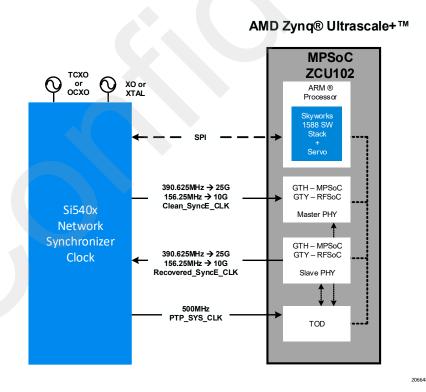

- The Si5518-A-FMC ships with 10GBASE-SR SFP+ transceivers, optical cable along with the required software on an SD card. FMC requires a customer-provided AMD ZCU102, ZCU111 or ZCU216 or ZCU670 FPGA evaluation board. FMC is only for AccuTime evaluation. Customers using the Si5512 should use the Si5518-A-FMC to evaluate AccuTime IEEE 1588 software.

<sup>\*</sup> See Ordering Guide table for current product revision.

Figure 1. Si5512 Ordering Guide Diagram

<sup>\*\* 5</sup> digits; assigned by ClockBuilder Pro for Custom OPN devices.

**DATA SHEET** Si5518

# 2. Ordering Guide

Table 1. Si5518 Ordering Guide

| Ordering Part Number<br>(OPN) <sup>1, 2, 3</sup> | Number of DSPLLs               | Number of<br>Outputs | Serial Interface        | AccuTime™<br>IEEE 1588<br>Software<br>Support <sup>4</sup> | Package                         | Temperature Range                                        |

|--------------------------------------------------|--------------------------------|----------------------|-------------------------|------------------------------------------------------------|---------------------------------|----------------------------------------------------------|

| Si5518A-Bxxxxx-GM                                | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire or 3-wire | No                                                         | 72-Lead QFN<br>10 x 10 mm       | -40 to 95 °C Ambient <sup>5</sup> -40 to 105 °C Board    |

| Si5518B-Bxxxxx-GM                                | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | -40 to 95 °C Ambient <sup>5</sup> -40 to 105 °C Board    |

| Si5518C-Bxxxxx-GM                                | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | I <sup>2</sup> C        | No                                                         | 72-Lead QFN<br>10 x 10 mm       | -40 to 95 °C Ambient <sup>5</sup> -40 to 105 °C Board    |

| Si5518D-Bxxxxx-GM                                | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | -40 to 95 °C Ambient <sup>5</sup> -40 to 105 °C Board    |

| Si5518E-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si5518F-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si5518G-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si5518H-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si5518I-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si5518P-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire or 3-wire | No                                                         | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si5518Q-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | SPI<br>4-wire only      | Yes                                                        | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si5518R-Bxxxxx-GM <sup>6</sup>                   | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | I <sup>2</sup> C        | No                                                         | 72-Lead QFN<br>10 x 10 mm       | –40 to 95 °C Ambient <sup>5</sup><br>–40 to 105 °C Board |

| Si55xx-A-EVB                                     | 1-RFPLL,<br>PPSPLL,<br>2-DSPLL | 18                   | _                       | _                                                          | Evaluation<br>Board             | -                                                        |

| Si5518-A-FMC-EVB <sup>7</sup>                    |                                | _                    | _                       | Yes                                                        | FPGA<br>Mezzanine Card<br>(FMC) | -                                                        |

<sup>1.</sup> Add an "R" at the end of the OPN to denote tape and reel ordering options.

Add an K at the end of the OPN to denote tape and rele ordering options.

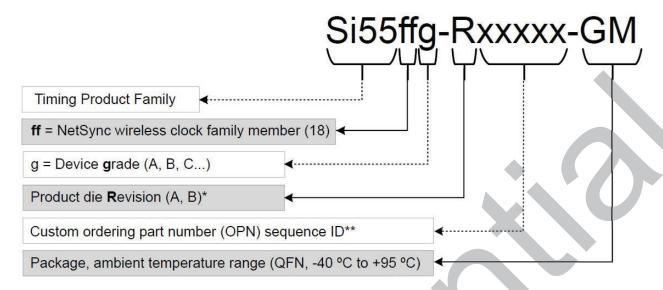

Custom, factory preprogrammed devices are available as well as unconfigured base devices. See the figure below for 5-digit numerical sequence nomenclature.

Revision B will be the device qualified for mass production and loose samples.

AccuTime IEEE 1588 software is only supported on certain part grades. Use this table to determine which grades support AccuTime.

Ambient temperature of 95 °C may not be possible with all configurations. This is dependent on device configuration. Tj cannot exceed a max of 125 °C.

Ambient exceed a may not be possible with an obligation. This is dependent on device configuration. If Calmid exceed a may of 123 °C.

Grades D, E, F, G, H, I, P, Q, and R are reserved for special factory use and not for general customer use.

The Si5518-A-FMC ships with 10GBASE-SR SFP+ transceivers, optical cable along with the required software on an SD card. FMC requires a customer-provided AMD ZCU102, ZCU111 or ZCU216 FPGA eval board. FMC is only for AccuTime evaluation.

DATA SHEET Si5518

<sup>\*</sup> See Ordering Guide table for current product revision.

5

Figure 2. Si5518 Ordering Guide Diagram

<sup>\*\* 5</sup> digits; assigned by ClockBuilder Pro for Custom OPN devices.

# 2. Ordering Guide

Table 1. Ordering Guide

| Ordering Part<br>Number (OPN) <sup>1,2</sup> | # of PLLs                                  | # of<br>Outputs | Serial Interface                         | AccuTime™ IEEE<br>1588 Software<br>Support <sup>3</sup> | Package                          | Temperature Range                                        |

|----------------------------------------------|--------------------------------------------|-----------------|------------------------------------------|---------------------------------------------------------|----------------------------------|----------------------------------------------------------|

| Si5403A-Axxxxx-GM                            | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | SPI 4-wire or 3-wire or I <sup>2</sup> C | No                                                      | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5403B-Axxxxx-GM                            | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead <b>QFN</b><br>10 x 10 mm | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5403C-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5403D-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5403E-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5403P-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | SPI 4-wire or 3-wire or I <sup>2</sup> C | No                                                      | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5403Q-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5402A-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 14              | SPI 4-wire only or I <sup>2</sup> C      | No                                                      | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5402B-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 14              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5402D-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 14              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5402E-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 14              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5402P-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 14              | SPI 4-wire only or I <sup>2</sup> C      | No                                                      | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5402Q-Axxxxx-GM <sup>5</sup>               | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 14              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5401A-Axxxxx-GM <sup>5</sup>               | 3 (REFPLL, DSPLL A and PPSPLL)             | 10              | SPI 4-wire only or I <sup>2</sup> C      | No                                                      | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5401B-Axxxxx-GM <sup>5</sup>               | 3 (REFPLL, DSPLL A and PPSPLL)             | 10              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5401D-Axxxxx-GM <sup>5</sup>               | 3 (REFPLL, DSPLL A and PPSPLL)             | 10              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5401E-Axxxxx-GM <sup>5</sup>               | 3 (REFPLL, DSPLL A and PPSPLL)             | 10              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5401P-Axxxxx- <b>GM</b> <sup>5</sup>       | 3 (REFPLL, DSPLL A and PPSPLL)             | 10              | SPI 4-wire only or I <sup>2</sup> C      | No                                                      | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si5401Q-Axxxxx-GM <sup>5</sup>               | 3 (REFPLL, DSPLL A and PPSPLL)             | 10              | SPI 4-wire only or I <sup>2</sup> C      | Yes                                                     | 72-Lead QFN<br>10 x 10 mm        | -40 to 95 °C Ambient <sup>4</sup><br>-40 to 105 °C Board |

| Si540X-A-EVB                                 | 4 (REFPLL, DSPLL A,<br>DSPLL B and PPSPLL) | 18              | _                                        | No                                                      | Evaluation Board                 |                                                          |

| Si5403-A-FMC-EVB <sup>6</sup>                | -                                          | _               | _                                        | Yes                                                     | FPGA Mezzanine<br>Card (FMC)     |                                                          |

<sup>1.</sup> Add an  ${\bf R}$  at the end of the OPN to denote tape and reel ordering options.

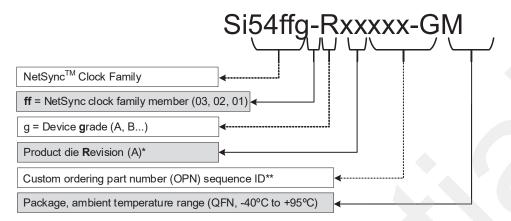

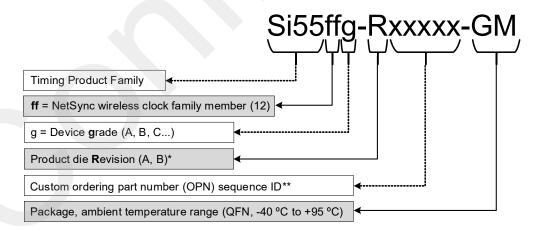

<sup>2.</sup> Custom, factory preprogrammed devices are available as well as unconfigured base devices. See the figure below for 5-digit numerical sequence nomenclature.

<sup>3.</sup> AccuTime IEEE 1588 software is only supported on certain part grades. Use this table to determine which grades support AccuTime.

<sup>4.</sup> Ambient temperature of 95 °C may not be possible with all configurations. This is dependent on device configuration. Tj cannot exceed a maximum of 125 °C.

<sup>5.</sup> Grades C, D, E, P, and Q are reserved for special applications. See ClockBuilder Pro for details.

<sup>6.</sup> The SiS403-A-FMC-EVB ships with 10GBASE-SR SFP+ transceivers, optical cable along with the required software on an SD card. FMC requires a customer-provided AMD ZCU102, ZCU111, or ZCU216 FPGA eval board. FMC is only for AccuTime evaluation.

<sup>\*</sup> See Ordering Guide table for current product revision.

206648-004

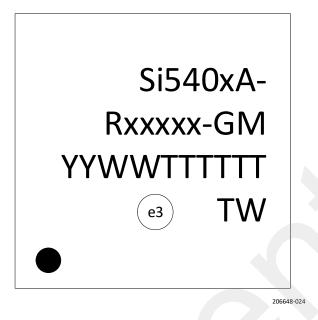

Figure 4. Ordering Guide

<sup>\*\* 5</sup> digits; assigned by ClockBuilder Pro for Custom OPN devices.

# **Datasheets**

- Si5510/08 Low-Phase-Noise, Jitter-Attenuating Clock for 5G/eCPRI

- Si5512: NetSync™ Low-Phase-Noise, Jitter-Attenuating Clock for 5G/eCPRI/SyncE/IEEE 1588

- Si5518 NetSync™ Low-Phase-Noise Jitter-Attenuating Clock for 5G/eCPRI/SyncE/IEEE 1588

- Si5403, Si5402, and Si5401: NetSync™ Network Synchronizer Clock for 5G, SyncE, and IEEE 1588 Applications

#### **DATA SHEET**

# Si5510/08 Low-Phase-Noise, Jitter-Attenuating Clock for 5G/eCPRI

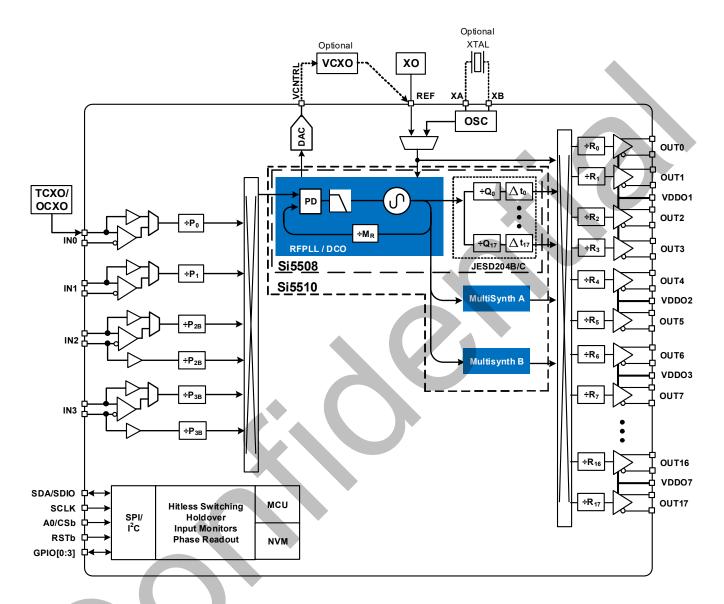

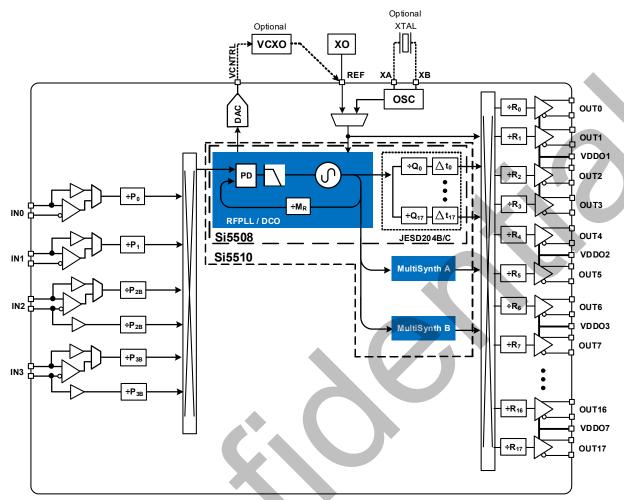

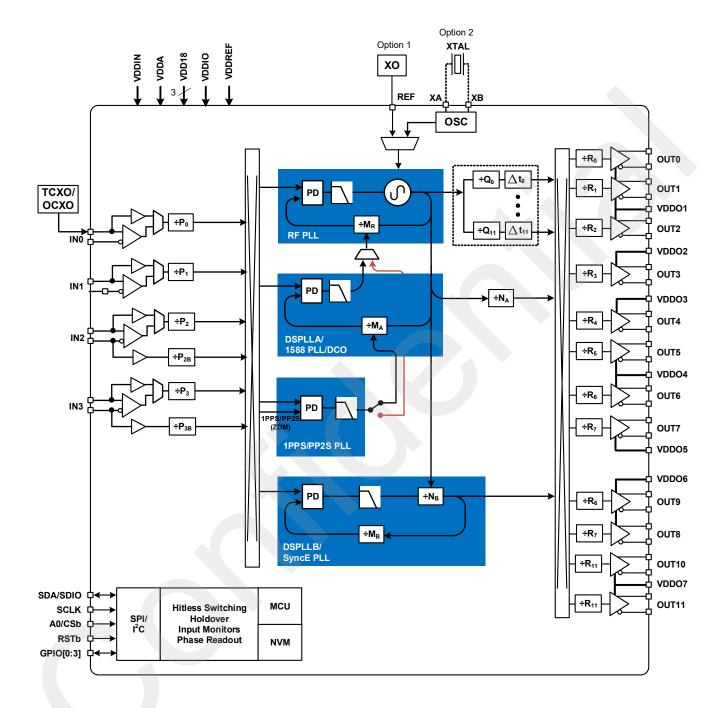

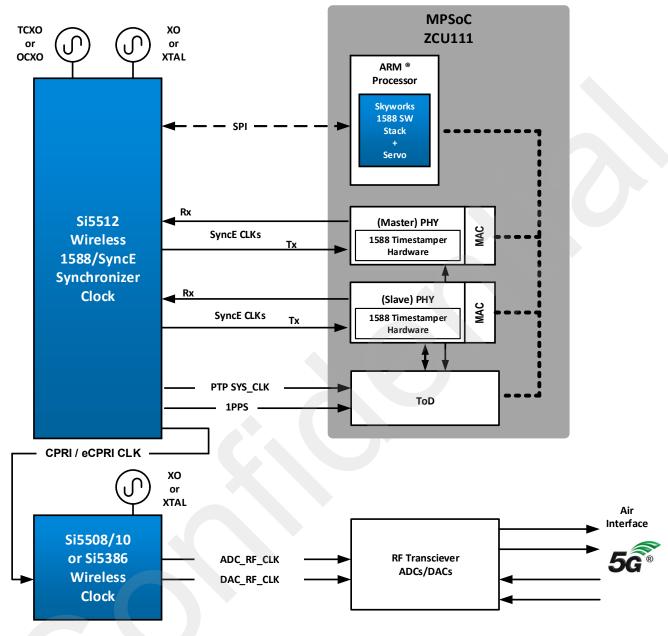

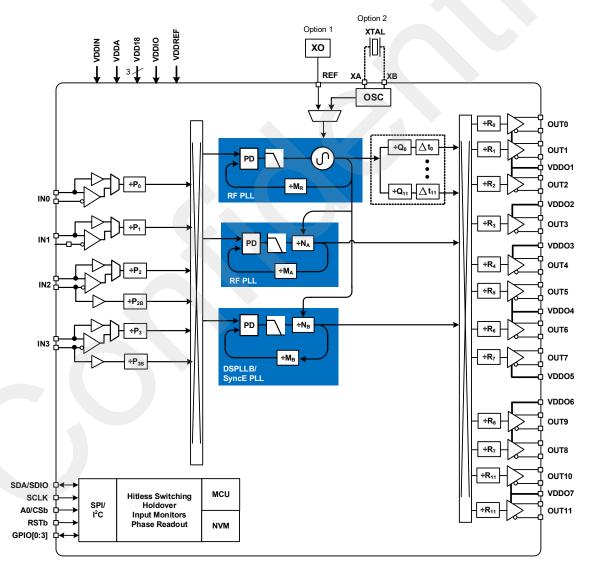

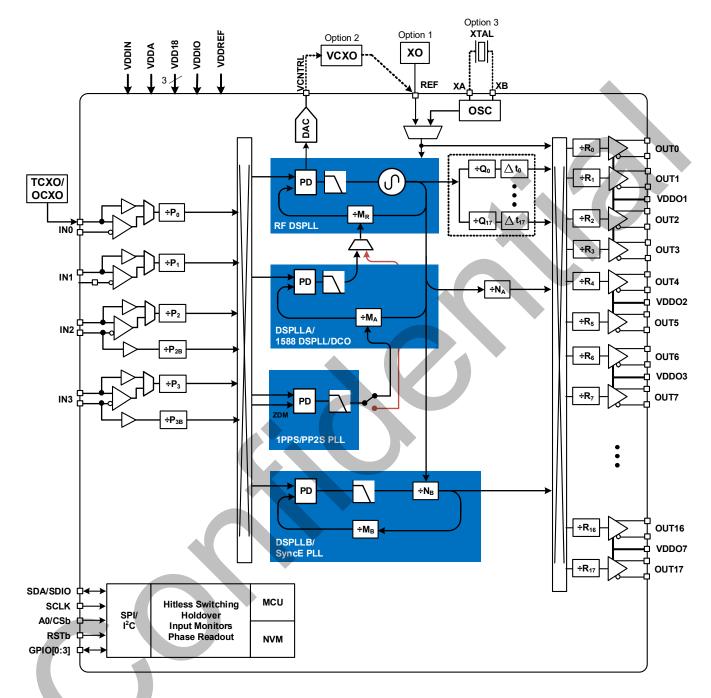

The Si5510/08 are low-noise, high-performance wireless jitter-attenuating clocks with any-frequency outputs for eCPRI (ethernet-based Common Public Radio Interface) applications. The Si5510/08 are based on Skyworks fifthgeneration DSPLL® technology, which combines frequency synthesis and jitter attenuation in a highly integrated digital solution with a cost-effective oscillator without the need for any external loop filter components.

A fixed frequency oscillator (XO or XTAL) provides a phase noise reference and frequency stability for free-run and holdover modes. A VCXO option is available for applications demanding the highest level of phase noise performance.

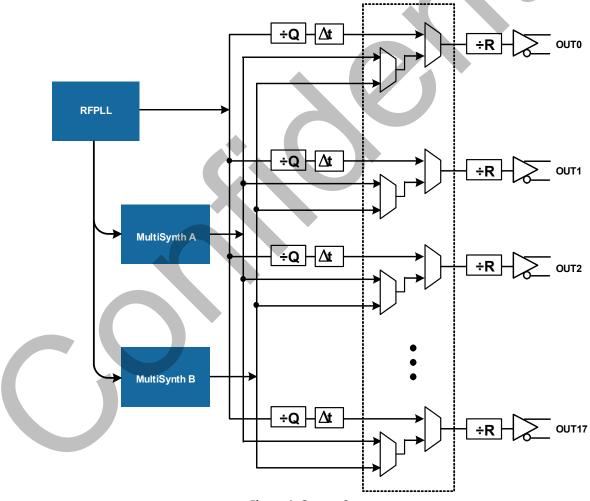

The RFPLL generates high performance low phase noise CPRI clocks for wireless remote radio heads (RRH). Each of the 18 clock outputs are configurable in any combination of high-performance JESD204B/C DCLK and SYSREF clock pairs, or other system clocks through the integer Q dividers. The RFPLL is a fully featured phase-locked-loop with adjustable DCO capability.

In addition to the RFPLL, the Si5510 integrates two lownoise MultiSynth™ fractional dividers. Any of the 18 clock outputs can be derived from either of the two MultiSynths.

# **Applications**

- LTE-A and 5G Remote Radio Units (RRU) or Active Antenna Units (AAU)

- JESD204B/C clock generation

- Remote Access Networks (RAN), picocells, small cells

- Remote Radio Heads (RRH), wireless repeaters, mobile fronthaul and backhaul

1

Skyworks Green™ products are compliant with all applicable legislation and are halogen-free. For additional information, refer to *Skyworks Definition of Green™*, document number SQ04–0074.

# **Key Points**

- Utilizes fifth-generation DSPLL® and MultiSynth™ technologies

- Ultra high-performance clock generation for LTE-A and 5G RRUs

- Integer output frequencies up to 3.2 GHz

- Fractional output frequencies up to 650 MHz

- JESD204B/C clock generation (DCLK/ SYSREF) with synchronization across multiple devices

- · Programmable delay at each output

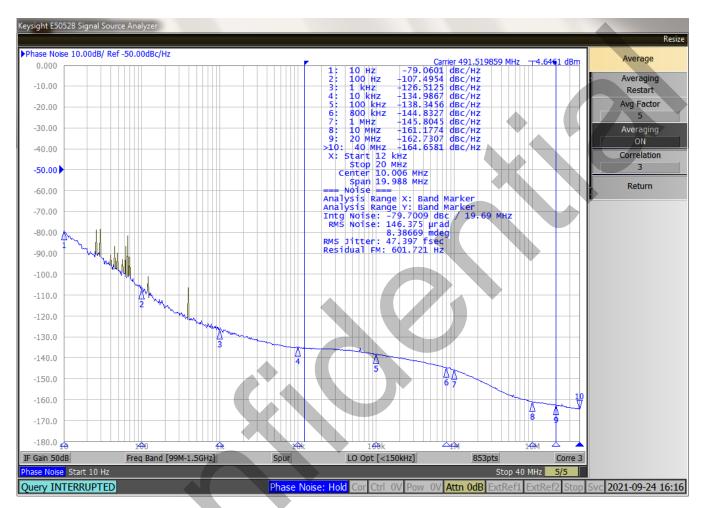

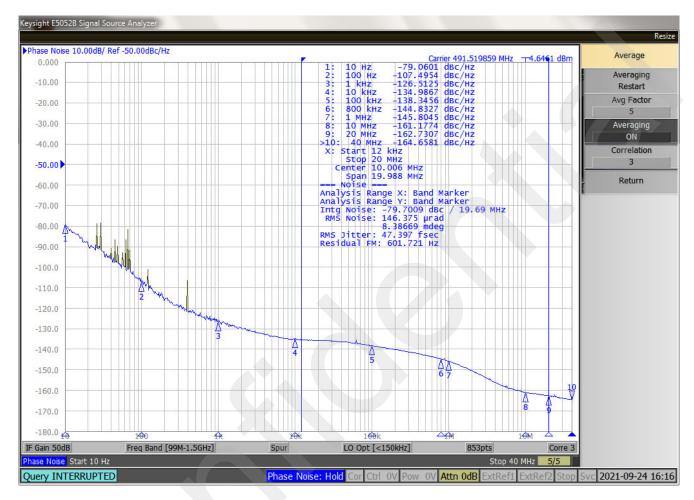

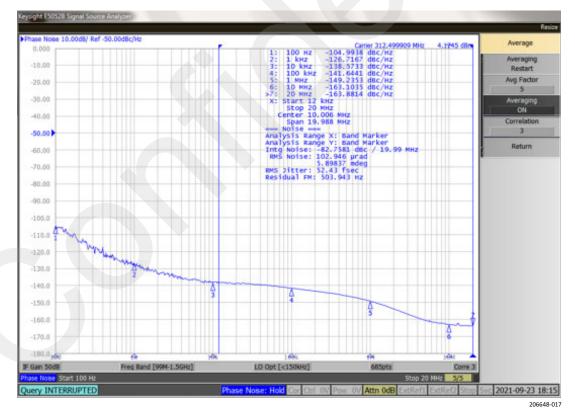

- Ultra-low jitter: 47 fs RMS typical

- Low-power mode

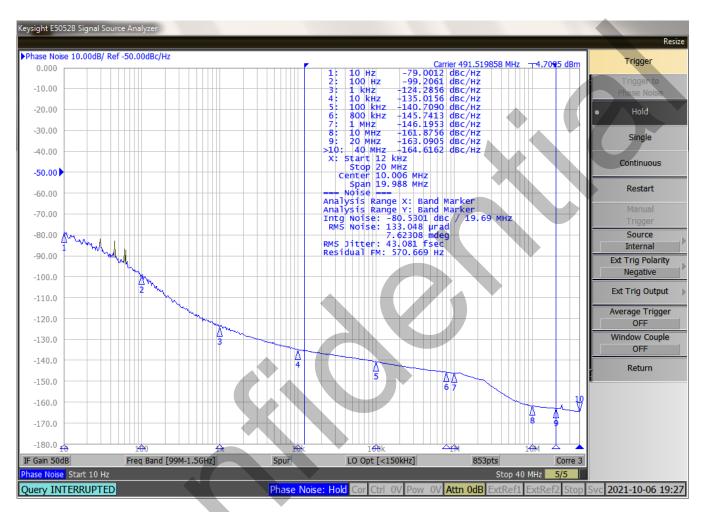

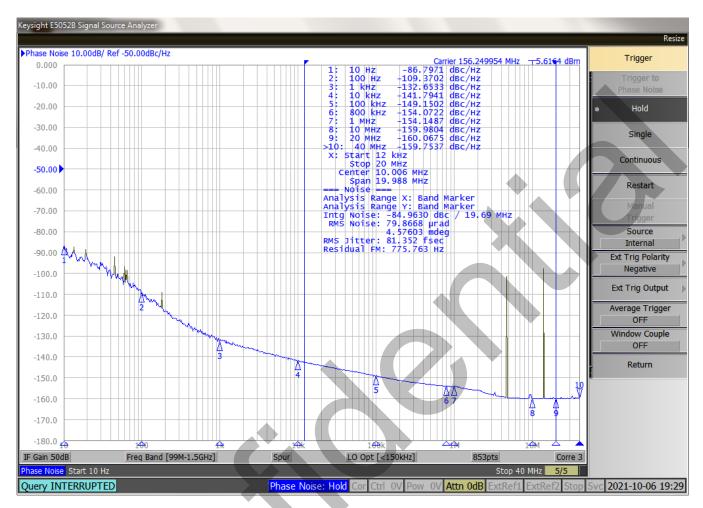

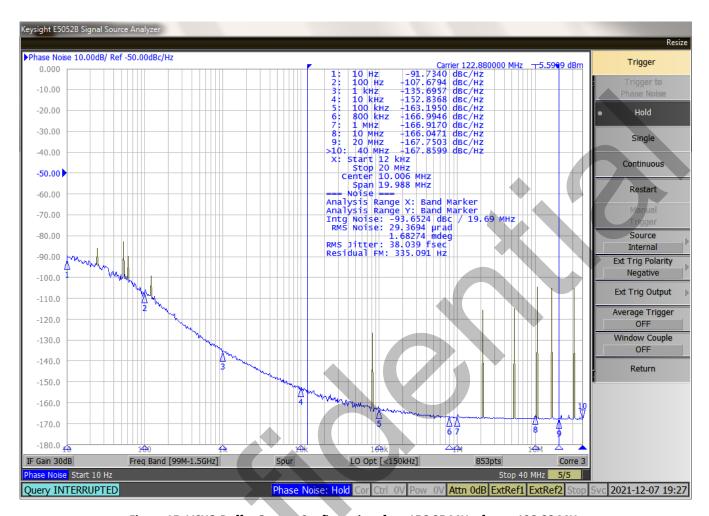

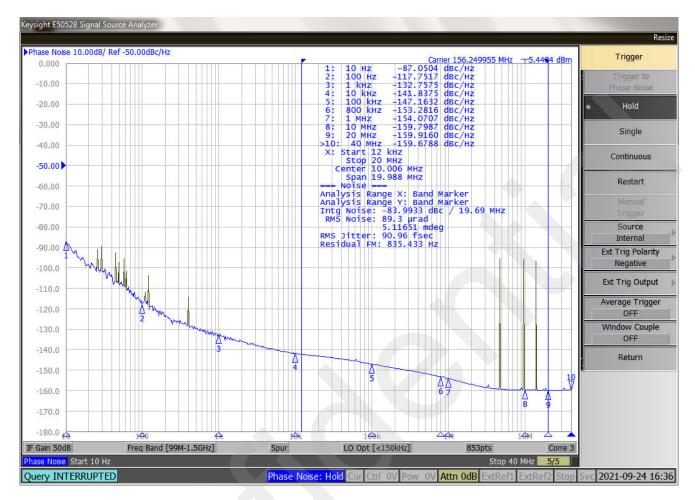

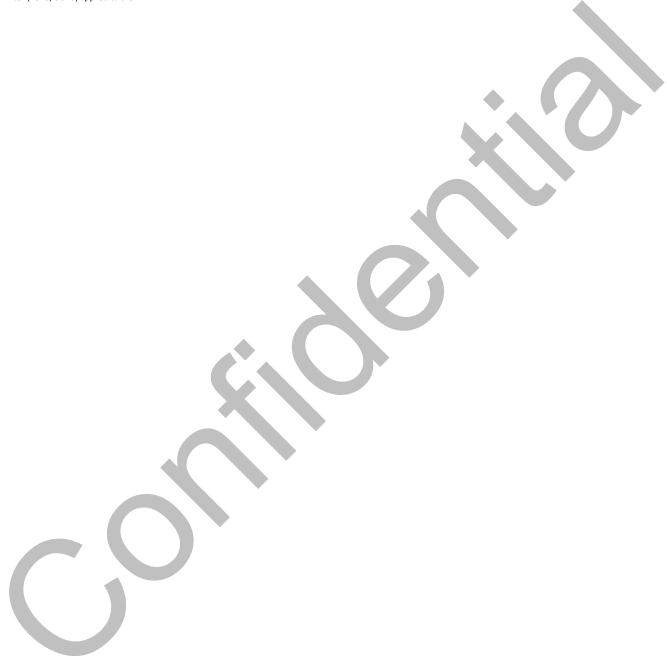

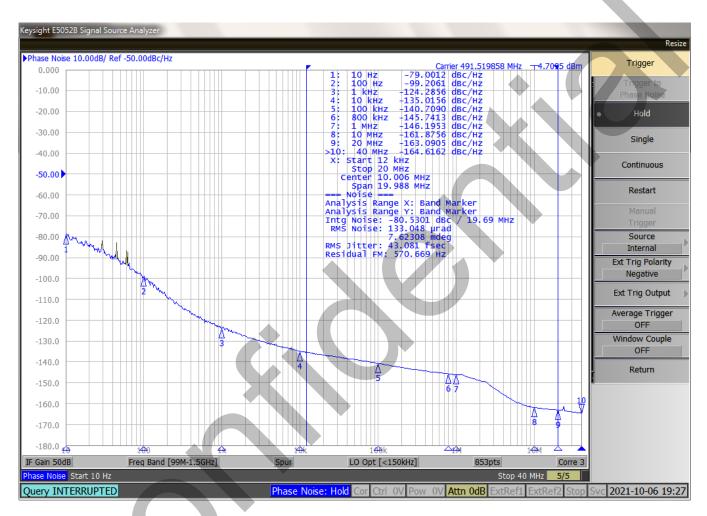

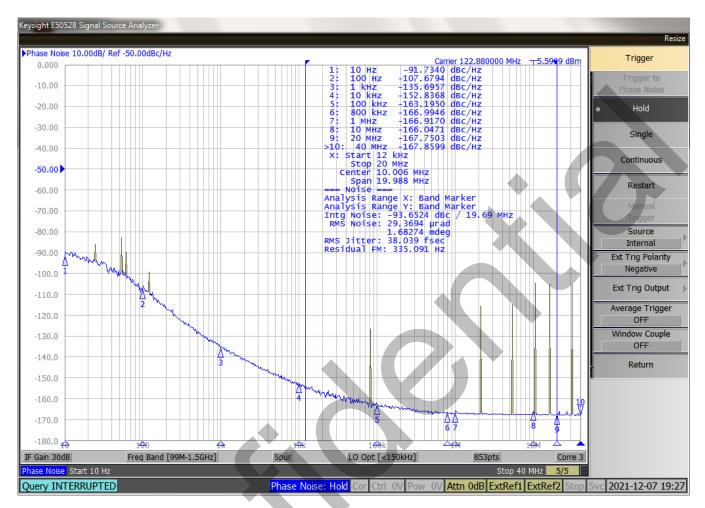

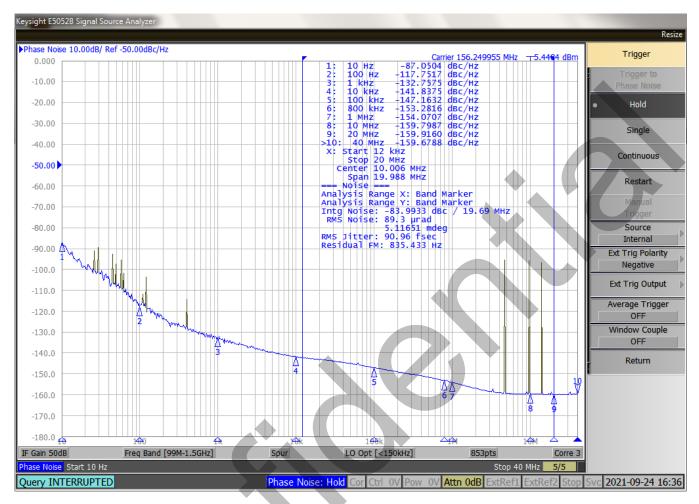

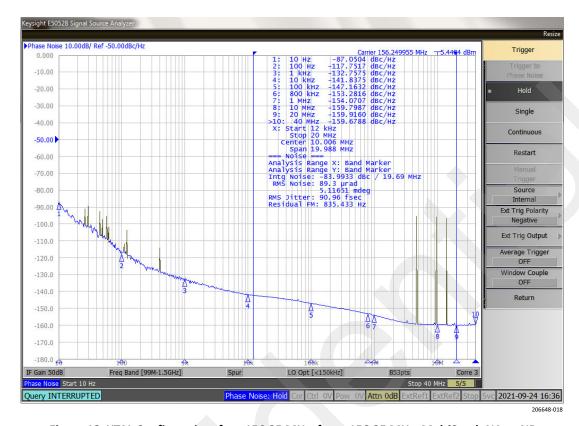

- Phase Noise:

- Noise floor -164 dBc/Hz at 491.52 MHz

- 145 dBc/Hz at 800 kHz offset for a 491.52 MHz carrier frequency

- Spurs < –95 dBc at 122.88 MHz</li>

- Supports DCO adjustable at 1 ppt resolution

- Full suite of status monitors

# **Block Diagram**

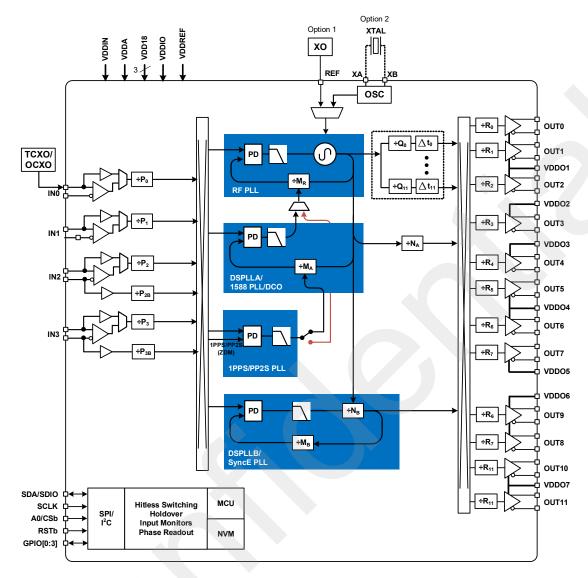

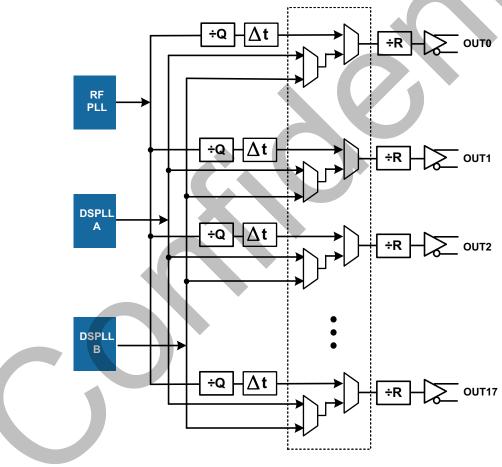

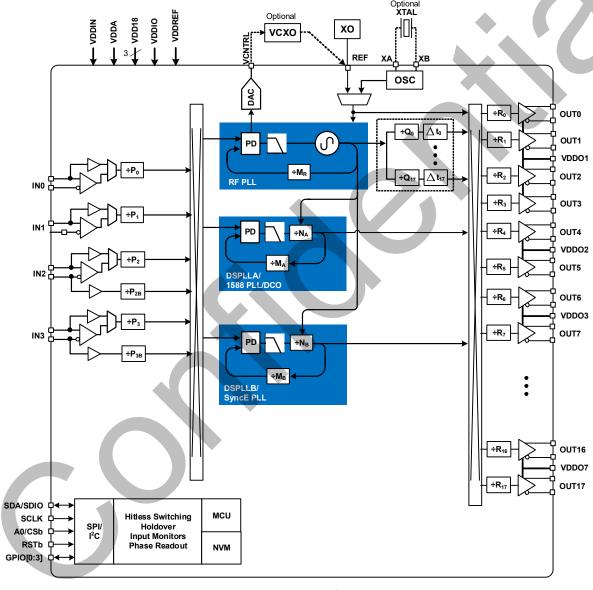

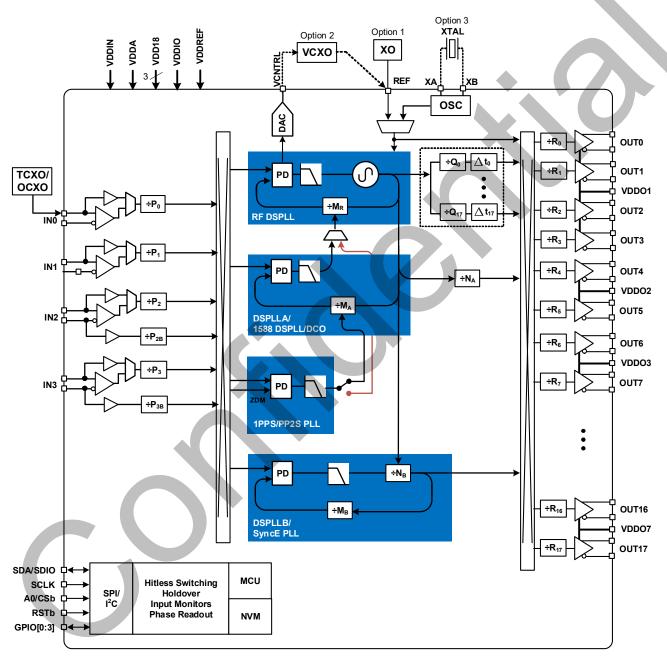

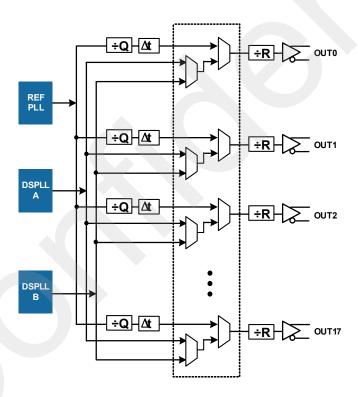

Figure 1. Si5510/08 Block Diagram

## 1. Feature List

- RFPLL

- Supports JESD204B/C Subclass 0, 1, and 2 Clocking

- Ultra-low Phase Noise (example at 491.52 MHz carrier):

- -164 dBc/Hz noise floor

- -145 dBc/Hz at 800 kHz offset

- Ultra-low jitter performance:

- <50 fs typ XO (12 kHz to 20 MHz at 491.52 MHz)

- <45 fs typ VCXO (12 kHz to 20 MHz at 491.52 MHz)

- Selectable jitter attenuation bandwidth: 10 Hz to 400 Hz

- Automatic Free-Run, Holdover, and Locked modes

- Hitless input clock switching: automatic or manual with < 150 ps phase transient</li>

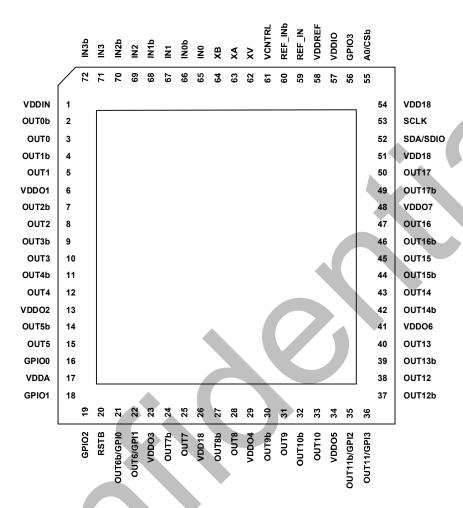

- 18 Programmable Clock Outputs:

- JESD204B/C DCLK or SYSREF. Up to nine DCLK/SYSREF pairs

- Integer Q dividers: PP2S/1PPS to 3.2 GHz

- JESD204B/C SYSREF pulser mode

- MultiSynth Fractional Dividers: PP2S/1PPS to 650 MHz

- Output-to-Output Static Delay: ±10 ns

- Output-output skew: ±50 ps

- LVDS, S-LVDS, ac-coupled LVPECL, LVCMOS, slew rate limited (SRL) LVCMOS, HCSL, CML

- Utilizes fifth-generation DSPLL® and MultiSynth technologies

- Zero Delay Mode

- 4/6 clock inputs:

- Differential: 8 kHz to 1 GHz

- CMOS: 8 kHz to 250 MHz

- Status monitoring (LOS, OOF, PHMON, FLOL and PLOL)

- Automatically generates free-running clocks at power up

- Automatically locks to a valid clock input

- Automatic holdover mode

- Core voltage: 3.3 V, 1.8 V

- Output driver supply voltages (VDDO): 3.3 V, 2.5 V, 1.8 V

- Serial Interface: I2C or SPI (3 or 4-wire)

- ClockBuilder® Pro (CBPro™) software tool simplifies device configuration

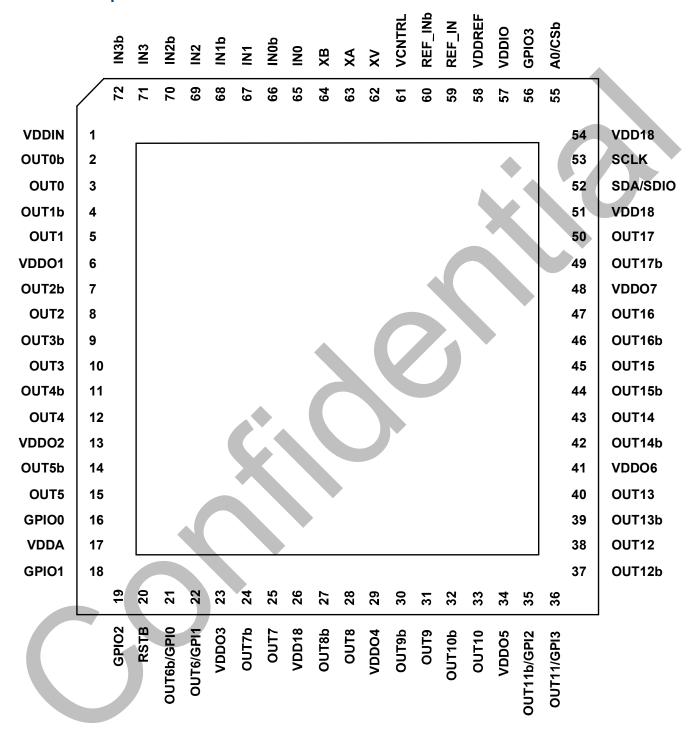

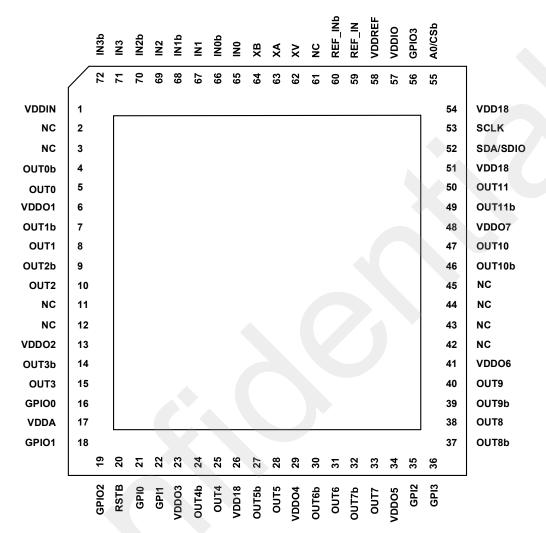

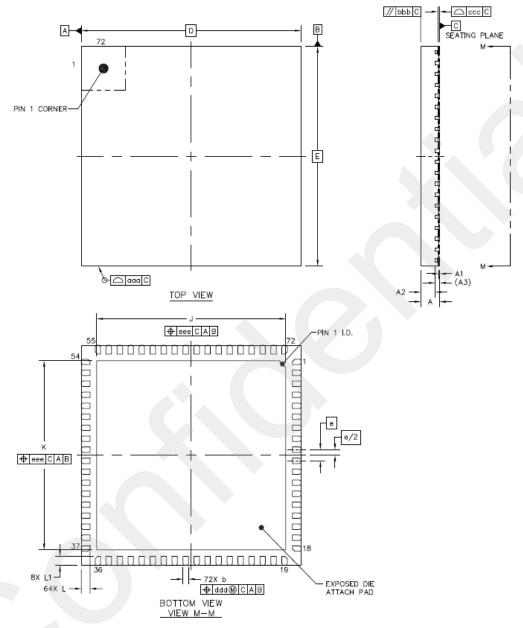

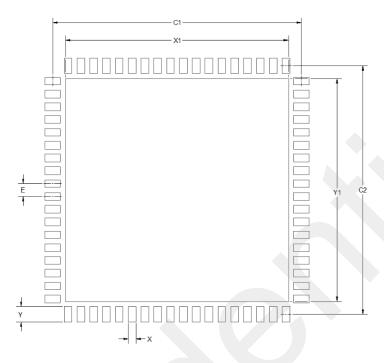

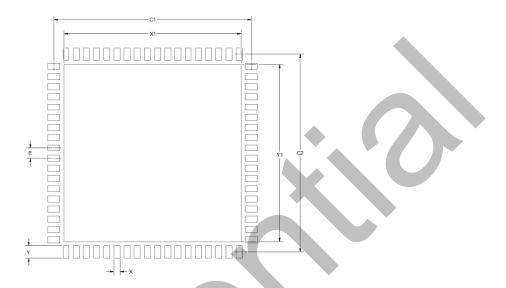

- Package: 72-Lead QFN, 10 x 10 mm

- Extended temperature range:

- -40 to +95 °C ambient

- -40 to +105 °C board

- Pb-free, RoHS compliant

Note: Specifications on this page are for reference only. Refer to Section 4. Electrical Specifications for device performance.

3

# 2. Ordering Guide

Table 1. Si5510/08 Ordering Guide

| Ordering Part Number (OPN) <sup>1, 2, 3</sup> | Number of DSPLLs,<br>MultiSynths | Number of<br>Outputs | Serial Interface        | Package                | Temperature Range                                        |

|-----------------------------------------------|----------------------------------|----------------------|-------------------------|------------------------|----------------------------------------------------------|

| Si5510A-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | –40 to 95 °C ambient<br>–40 to 105 °C board <sup>5</sup> |

| Si5510C-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | 12C                     | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5510D-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | 12C                     | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5510E-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>2-MultiSynths         | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | -40 to 95 °C ambient<br>-40 to 105 °C board <sup>5</sup> |

| Si5508A-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>No-MultiSynths        | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | –40 to 95 °C ambient<br>–40 to 105 °C board <sup>5</sup> |

| Si5508C-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>No-MultiSynths        | 18                   | 12C                     | 72-Lead QFN 10 x 10 mm | –40 to 95 °C ambient<br>–40 to 105 °C board <sup>5</sup> |

| Si5508D-Bxxxxx-GM <sup>4</sup>                | 1-RFPLL<br>No-MultiSynths        | 18                   | SPI<br>4-wire or 3-wire | 72-Lead QFN 10 x 10 mm | –40 to 95 °C ambient<br>–40 to 105 °C board <sup>5</sup> |

| Si55xx-A-EVB <sup>6</sup>                     | _                                | 18                   |                         | Evaluation board       | _                                                        |

- 1. Add an "R" at the end of the OPN to denote tape and reel ordering options.

- 2. Custom, factory preprogrammed devices are available. See the figure below for 5-digit numerical sequence nomenclature.

- 3. Revision B will be the device qualified for mass production and loose samples.

- 4. Grade D and E are reserved for special applications, see CBPro for details.

- 5. Si55xx EVB can be configured as either Si5510 or Si5508.

- 6. Si55xx-A-EVB can be configured as either Si5510 or Si5508.

<sup>\*</sup> See Ordering Guide table for current product revision.

Figure 2. Si5510/08 Ordering Guide Diagram

<sup>\*\* 5</sup> digits; assigned by ClockBuilder Pro for Custom OPN devices.

# 3. Functional Description

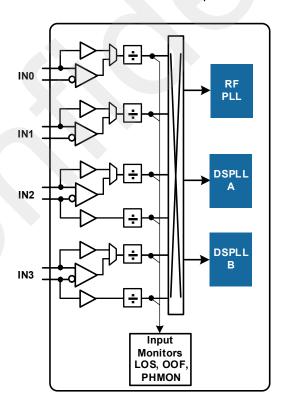

The Si5510/08 are high-performance JESD204B/C compatible RF clock jitter attenuators incorporating a fifth-generation RFPLL, with low noise Q-Divider outputs or up to two low-noise MultiSynths that generate integer or fractionally related output frequencies. These devices have integrated programmable loop filters and on-chip LDOs that provide excellent supply noise rejection requiring only a few external components. The RFPLL can operate from an external VCXO, XO or fixed frequency crystal (XTAL), known as single reference mode. The RFPLL supports Locked, Free-Run, and Holdover modes of operation with an optional DCO mode. There are four differential or six single-ended inputs available to the RFPLL. Two of the inputs (IN2, IN3) can be configured as dual single-ended inputs in applications where more than four inputs are required. Input selection can be manual or automatically controlled using an internal state machine. Any of the 18 output clocks (OUT0 to OUT17) can be sourced from any of the output dividers using a flexible crosspoint connection.

# 3.1. Frequency Configuration

The frequency configuration of the RFPLL is programmable through the serial interface and can also be stored in non-volatile memory. The combination of input dividers (P), fractional frequency multiplication (M), integer output division (Q), fractional output division (N), and integer output division (R) allows the generation of virtually any output frequency on any of the outputs. All divider values for a specific frequency plan are automatically calculated using the CBPro™ utility.

## 3.2. RFPLL Loop Bandwidth, Initial Lock, and Fast Lock Settings

The RFPLL loop bandwidth determines the amount of input clock jitter attenuation. The RFPLL will always remain stable with low peaking regardless of the loop bandwidth selection.

The RFPLL has configurable loop bandwidths. There are three configurations; each has a separate setting for the loop bandwidth:

- Initial Lock Bandwidth: The PLL uses this bandwidth when it exits Free-Run Mode and attempts to lock to a new input clock.

- Loop Bandwidth: This sets the bandwidth of the PLL once lock to an input is achieved.

- Fastlock Bandwidth: This sets the bandwidth of the PLL when exiting from holdover.

Selecting a low RFPLL loop bandwidth will generally lengthen the lock acquisition time. The Fastlock feature allows setting of a temporary Fastlock Loop Bandwidth that is used during the lock acquisition process. The RFPLL will revert to its normal loop bandwidth once lock acquisition has completed.

See the Si5518/12/10/08 Reference Manual and CBPro for more information, recommendations, and limits for setting PLL loop bandwidths for different configurations.

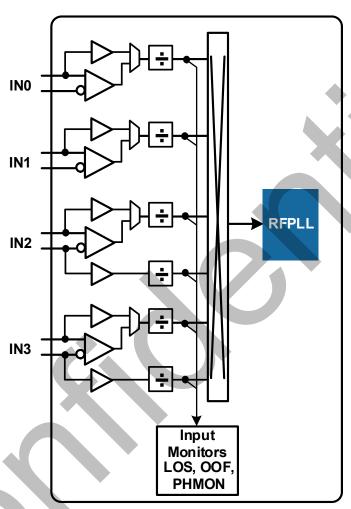

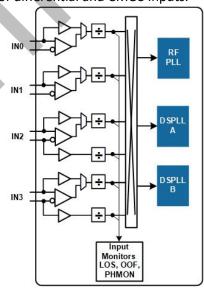

## 3.3. Inputs

There are four differential inputs which can also be configured as single-ended CMOS inputs. Both INO and IN1 can support a single CMOS input, while IN2 and IN3 can be configured as dual CMOS inputs. This allows support for up to 6 CMOS inputs, or any combination of differential and CMOS inputs.

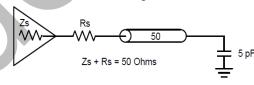

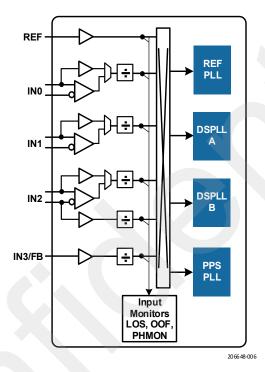

Figure 3. Input Structure

### 3.3.1. Input Terminations

Refer to AN1293: Si55xx Schematic Design and Board Layout Guidelines and the Si5518/12/10/08 Reference Manual for guidance on input terminations.

### 3.3.2. Input Selection

Input selection of the RFPLL can be controlled manually through pin control, API command, CLI command, or automatically using an internal state machine.

#### 3.3.2.1. Input Divider

The device utilizes both fractional and integer input (P) dividers to lock to any frequency input clock. The CBPro software chooses the optimum divide values based on the user-defined frequency plan. Each input divider (P0, P1, P2, P2b, P3, and P3b) can be configured independently of the others.

#### 3.3.2.2. Manual Input Selection

In manual mode, the input selection is made by defining a GPIO pin as an input select pin and changing the input pin voltage level, or by writing an API or CLI command. Any of the inputs are available to the RFPLL through a crosspoint input selection switch. If there is no clock signal on the selected input, or if the input is not valid due to LOS/OOF/PHMON input alarms, the RFPLL will automatically enter Free-Run/Holdover Mode.

#### 3.3.2.3. Automatic Input Selection

When configured in this mode, the RFPLL automatically selects a valid input that has the highest configured priority. The priority scheme is independently configurable and supports revertive or non-revertive selection. All inputs are continuously monitored for loss of signal (LOS), invalid frequency range (OOF), and phase (PHMON). Only valid inputs that have no LOS, OOF or phase monitor (PHMON) alarms can be selected by the automatic state machine. The RFPLL will enter Free-Run or Holdover Mode if there are no valid inputs available.

#### 3.3.3. Unused Inputs

Unused inputs should be configured as "Unused (Powered Down)" and the pins may be left unconnected or accoupled to ground. See AN1293: Si55xx Schematic Design and Board Layout Guidelines and the Si5518/12/10/08 Reference Manual for recommendations on how to minimize system noise on any CMOS input and or any differential input configured as "Enabled" but not actively being driven by a clock.

#### 3.3.4. Phase Readout (PHRD)

The phase readout Device API command can be used to measure the phase difference between different input clocks to the Si5510/08. Unused inputs that are not assigned to the RFPLL can also be configured as phase readout (PHRD) or phase readout feedback (PHRD\_FB) inputs. These inputs can be used to measure the phase of an output of the Si5510/08 to the input(s) of known phase. PHRD and PHRD\_FB inputs use the same alarms, such as LOS/OOF/PHMON, as the other clock inputs, but they are not assigned to the PLL.

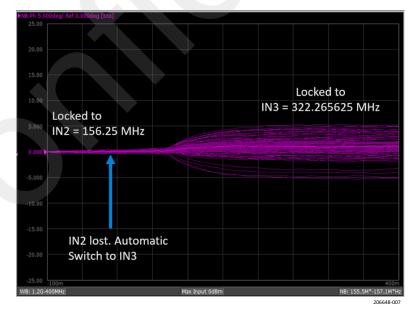

# 3.4. Input Clock Switching

Clock inputs applied to the Si5510/08 can be either from the same source (0 ppm, same nominal frequency) or different sources (non-0 ppm, different nominal frequencies). The Si5510/08 automatically determines the optimal switching mode depending on the nominal frequency difference between the clocks at the time of the switch. When switching between 0 ppm inputs, the Si5510/08 performs either a hitless switch with phase buildout (PBO) or a phase pull-in (PPI) switch depending on the user selection in CBPro. When the input clocks have a non-0 ppm offset, the Si5510/08 performs a frequency-ramped input switch.

Refer to the Si5518/12/10/08 Reference Manual for additional guidance on input clock switching modes. All input clock switches are glitchless, which means that no runt pulses are generated at the output during the transition.

## 3.4.1. Hitless Input Switching for 0 ppm Clocks-Phase Buildout (PBO)

Applications like eCPRI require that transients are kept to a minimum when switching between input clocks. Hitless switching with phase buildout (PBO) is a feature that prevents a transient from propagating to the output when switching between two clock inputs that have a fixed phase relationship. A hitless switch can only occur when the two input frequencies are frequency locked, meaning that the nominal frequencies are the same (0 ppm). Due to the nature of hitless switching, the input-to-output delay of the RFPLL is not preserved. The RFPLL simply absorbs the phase difference between the two input clocks during an input switch.

### 3.4.2. Phase Pull-In (PPI) Input Switching for 0 ppm Clocks

In some applications, such as traditional CPRI fronthaul clocking, the output phase must track the input phase with minimal delay. When the application requires the input-to-output delay to be preserved after clock switching, the phase pull-in clock switching mode should be selected. In this mode, the output phase will be pulled in at a user-programmable ramp rate referred to as the PPI slope (ns/s). With phase pull-in switching, the output phase always aligns with the newly selected input. PPI is always enabled for zero-delay mode applications.

#### 3.4.3. Ramped Input Switching for Non-0 ppm Clocks

The ramped switching feature allows the RFPLL to switch between two input clock frequencies that have a non-Oppm offset without an abrupt frequency transient at the output. When the two input clock frequencies are not the same nominal frequency, the RFPLL will pull in the frequency difference between inputs at the ramp rate that is programmable in CBPro from ppb/s to ppm/s. The loss-of-lock (LOL) and LOOP\_FILTER\_RAMP\_IN\_PROGRESS indicators (accessible through the Device API) will assert while the RFPLL is ramping to the new clock frequency.

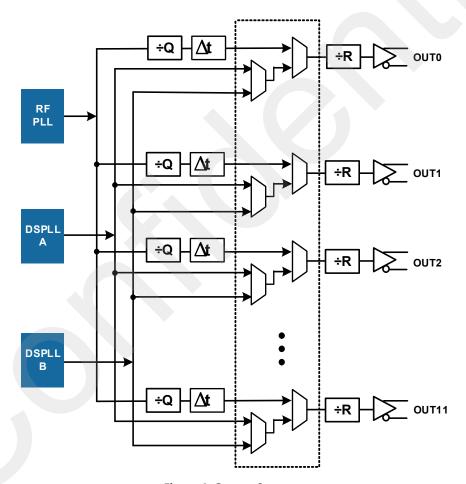

# 3.5. Outputs

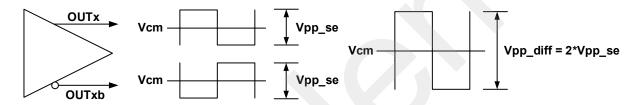

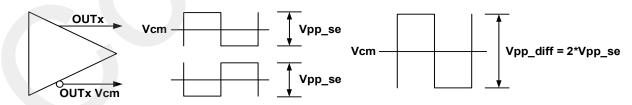

The Si5510/08 supports 18 differential output drivers configurable as AC Coupled LVPECL, LVDS, S-LVDS, CML, HCSL, LVCMOS, or SRL LVCMOS. When in LVCMOS mode, the differential pair becomes two single-ended outputs for a maximum of 36 possible outputs. Two of the output drivers (OUT16 and OUT17) have slew rate control when in LVCMOS mode. This allows limiting the rise time of the output signal to reduce the possibility of crosstalk to adjacent output drivers. The outputs have power supply pins (VDDOx) for output driver groups of 4-2-2-2-4-2, which can be individually powered by 3.3, 2.5, or 1.8 V. The LVCMOS output voltage is set by the VDDOx pin. Refer to Table 18, Pin Descriptions.

## 3.5.1. Output Crosspoint

A crosspoint allows any of the output drivers to connect with its associated Q divider or either of the MultiSynths. A digital output delay adjustment is possible on each of the Q divider outputs for JESD204B/C applications. The static delay adjustments are programmable and may be stored in NVM so that the desired output configuration is ready at power up.

Figure 4. Output Structure

# 3.5.2. Differential and LVCMOS Output Terminations

Refer to AN1293: Si55xx Schematic Design and Board Layout Guidelines and the Si5518/12/10/08 Reference Manual for guidance on output terminations.

#### 3.5.3. Slew Rate Limited (SRL) LVCMOS Outputs

The swing of LVCMOS and SRL LVCMOS outputs is rail-to-rail; so, the swing is determined by the voltage of the corresponding VDDO pin of the LVCMOS or SRL LVCMOS output. Each output driver configured as LVCMOS or SRL LVCMOS has two outputs, OUTx/OUTxb. The polarity of each of the two outputs may be independently configured as a noninverted or inverted output as well as enabled or disabled.

OUT16/16b and OUT17/17b may be configured as SRL LVCMOS outputs, which have a selectable slew rate and generate significantly less crosstalk than conventional LVCMOS outputs, which is useful in jitter-critical applications.

SRL LVCMOS output clocks on OUT16/16b and OUT17/17b are intended only for low frequency clock applications. Refer to the Si5518/12/10/08 Reference Manual for the maximum Fout supported for each slew rate selection.

## 3.5.4. Output Enable/Disable

Each output driver may be enabled/disabled through programmable GPIO pins. There are two output enable groups, OEO and OE1, which are logically OR'ed together to determine which outputs are enabled at any point in time. CBPro allows the control and selection of the GPIO pin mapping to the outputs.

Outputs may also be enabled/disabled using the device API. If an output is assigned as GPIO controlled, it cannot be controlled via the API. The API controlled output enable allows for more flexibility than the GPIO control as any of the outputs can be individually enabled/disabled via an API command.

The default output enable/disable behavior is a glitchless enable/disable. For clocks to start or stop as soon as possible, accepting runt pulses or glitches, instant output enable/disable can be used.

#### 3.5.5. State of Disabled Output

The disabled state of an output driver may be configured as stop high, stop low, or Hi-Z. CMOS outputs <2 MHz can also be configured as Hi-Z with weak pullup/down.

Differential outputs, when disabled, will maintain the output common-mode voltage even while the output is not toggling. This minimizes disturbances when disabling and enabling clock outputs.

### 3.5.6. Output Dividers

The device utilizes both integer Q dividers and fractional NA, NB MultiSynth output dividers. The ClockBuilder Pro software chooses the optimal divide values based on the user-defined frequency plan.

A summary of each class of divider is listed below:

Output Q Divider: Q0-Q17

Integer Only Divide Value

Output N Divider: NA, NB

- MultiSynth Divider, Integer or Fractional Divide Value

3. Output Divider: R17-R0Integer Only Divide Value

#### 3.5.7. Output Skew Control

Output skew control allows outputs that are derived from the Q dividers to be phase adjusted in steps of 1/fvco or 1/(4\*fvco) when the fine adjust is enabled. The exact skew adjustment and step sizes are reported on the Output Skew Control Tab of the CBPro Wizard.

#### 3.5.8. Output Synchronization (OSYNC)

The OSYNC input is used to align the phases of the integer Q divider output clocks to a SYNC input signal from a logic device (ASIC/FPGA) or a data converter. OSYNC can be used to achieve deterministic latency in a JESD204B/C Subclass 2 application. When asserted, the Q divider outputs will stop low glitch-free. When OSYNC is deasserted, the first transition of all outputs will be aligned to the OSYNC signal within the data sheet delay from OSYNC de-asserted to output reenabled specification. OSYNC must be assigned to GPIO2.

OSYNC can also be used to align the phases of the Q divider output clocks between multiple Si5510/08 devices to a SYNC input signal. To achieve the chip-to-chip data sheet specification for output skew, the input clock to the Si5510/08 must be a CPRI frequency (N\*1.92 MHz) and integer-related to the Q divider outputs.

OSYNC can also be initiated through an API command instead of a GPIO input; however, the OSYNC de-asserted to output reenabled specification cannot be guaranteed. The API command should not be used for multichip OSYNC.

### **3.6. RFPLL**

The RFPLL controls the central VCO which provides many of the essential functions for the device such as generating ultra-low phase noise JESD204B/C clocks and maintaining free-run accuracy and holdover stability. It operates using one of many external frequency sources. A simple low-cost fixed frequency crystal (XTAL) provides the phase noise reference and the RFPLL locks to a clock input for jitter attenuation. Options of using a crystal oscillator (XO) or a voltage-controlled crystal oscillator (VCXO) are also available. The benefits and trade-offs of the phase noise reference are covered in the Si5518/12/10/08 Reference Manual and CBPro.

#### 3.6.1. JESD204B/C Clock Generation

The RFPLL generates ultra-low phase noise JESD204B/C clocks for Subclass 0, Subclass 1, and Subclass 2 operation. Any of the 18 clock outputs can be assigned to generate JESD204B/C output clocks.

JESD204B/C Subclass 0 and Subclass 2 support is provided through the OSYNC input assignable to GPIO2.

JESD204B/C Subclass 1 support is provided with assignable SYSREF/DCLK timing skew, as well as with a SYSREF pulser that supports JESD204B/C "gapped" periodic outputs.

Static delay is assignable with a step size down to 1/4\*VCO period (approximately 20 ps). Exact delay is reported in CBPro.

Each SYSREF output can be configured in continuous mode. SYSREFS in continuous mode may cause crosstalk with adjacent DCLK outputs. If using SYSREF in continuous mode a gap of one unused output is recommended between SYSREF and DCLK.

The SYSREFs can also be configured in pulsed mode. The SYSREF pulser provides 1, 2, 4, 8, 16, or 32 pulses on user request, with the SYSREF held static between requests. SYSREFs in pulsed mode will not couple with other channels since for the majority of operation they are disabled. A gap or unused output between DCLK and SYSREF is

not necessary in pulsed mode. Each SYSREF can be independently assigned as Continuous or Pulsed mode with desired number of pulses in CBPro. A common SYSREF pulse request for all pulsed SYSREF outputs can be initiated either by a rising edge on assignable digital input SRCREQ, or by using the JESD\_SYSREF\_PULSER API via the serial interface.

#### 3.7. DCO Mode

The RFPLL DCO can be frequency controlled in pre-defined steps ranging from <1 ppt to several ppm. The DCO can be controlled when the RFPLL is locked to an external clock or when it is in Free-Run/Holdover mode. The frequency adjustments are controlled through the serial interface by triggering a Device API command or by pin control using frequency increments (FINC) or decrements (FDEC). Both the FINC and FDEC pins are available through the configurable GPIO pins. A FINC will add the frequency step word to the PLL output frequency, while a FDEC will decrement it. Step sizes are configured in CBPro.

### 3.8. Zero Delay Mode (ZDM)

Zero delay mode (ZDM) is a mode of operation in which more accurate input-to-output phase delay can be achieved on the RFPLL by providing an external feedback from one of the clock outputs to one of the clock inputs. For more details on implementing ZDM, see AN1293: Si55xx Schematic Design and Board Layout Guidelines and the Si5518/12/10/08 Reference Manual.

## 3.9. External Reference Clocks (XA/XB, REF IN)

The Si5510/08 operates from either an external crystal oscillator (XO) connected to the REF\_IN pins or with an optional fixed-frequency crystal (XTAL) connected to the XA, XB pins. The internal oscillator (OSC) combined with a low cost external XTAL produces an ultra-low jitter reference clock for the RFPLL. When using an external XO, it's important to select one that meets the jitter performance requirements of the end application. Alternatively, the device can operate with an external voltage-controlled crystal oscillator (VCXO). Operating the device with only an XO or XTAL, or with only a VCXO is referred to as single reference mode, as shown in Figure 5, "Single Reference Mode," on page 13. The low phase noise reference XO/VCXO or XTAL is connected to REF\_IN or XA/XB.

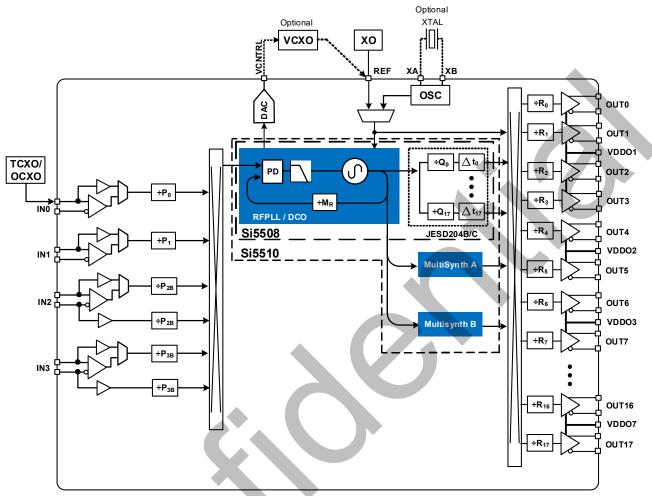

The Si5510/08 can also be configured in a dual reference clock generator mode where a TCXO or OCXO provides improved frequency stability. In this case, the RFPLL locks to a TCXO or OCXO that is applied to one of the inputs. This mode is referred to as dual reference clock generator mode since the output frequencies track the TCXO or OCXO frequency. It is possible to DCO the RFPLL in dual reference clock generator mode. This configuration is shown in Figure 6, "Dual Reference Clock Generator Mode," on page 14. The low phase noise reference XO/VCXO or XTAL is connected to REF\_IN or XA/XB as described above.

Use CBPro to configure the device in either single reference mode or dual reference clock generator mode.

Figure 5. Single Reference Mode

Figure 6. Dual Reference Clock Generator Mode

## **3.9.1. XA, XB Inputs**

The XA/XB inputs are used to provide a fixed frequency reference for the RFPLL. The device includes internal XTAL loading capacitors which eliminate the need for external capacitors and also has the benefit of reduced noise coupling from external sources. A crystal in the range of 48 to 54 MHz is recommended for best jitter performance.

## 3.9.2. **REF\_IN Input**

An alternative to using an external XTAL is to connect a crystal oscillator (XO) directly to the REF\_IN Input. Another option is using an external voltage controlled crystal oscillator (VCXO). In VCXO mode, the RFPLL produces an analog control voltage which adjusts the VCXO's output frequency. This mode is useful when generating specific integer related output frequencies such as in wireless applications (e.g., 4G/LTE, 5G). The REF\_IN inputs accommodate both single-ended CMOS as well as differential XOs/VCXOs. See the Si55xx, Si540x, and Si536x Recommended XTAL, XO, VCXO, TCXO, and OCXO Reference Manual for more information.

#### 3.9.3. VCXO Buffer Output

When the REF\_IN input is a VCXO, there is a VCXO buffer output available that can be used to achieve the lowest midband phase noise (10 kHz to 1 MHz). This is often critical for high-end applications, such as mmWave. The VCXO buffer output tracks the phase and frequency of the input clock just as any of the other Si5510/08 outputs. However, since the VCO and Q dividers are bypassed, the buffer output frequency must equal the frequency of the VCXO. All of the remaining outputs and RFPLL are still available when using buffer output. The buffer output can be assigned to any of the outputs via the output crosspoint mux. The buffer output is not available when using an XO or XTAL.

#### 3.10. GPIO Pins (General Purpose Input or Output)

There are four GPIO pins which have programmable functions. They can be assigned as either an input or an output from one of the functions shown in the table below. OUT6/11 can be repurposed as GPIs when they are not being used as clock outputs.

The GPIs are programmable as either active high or active low via ClockBuilder Pro. Active low GPIs are indicated by adding a "b" at the end of the function name for example "OEb" as displayed in ClockBuilder Pro. All GPI pins have a weak pull-up (PU) or pull-down (PD) resistor to set a default state when not externally driven. The default state of the GPI is always de-asserted except for OEx, which is, by default, asserted to enable the outputs. The internal resistance of the PU/PD resistor is  $20 \text{ k}\Omega$  typical.

GPIO selectable status outputs (GPO) are push-pull and do not require any external pull-up or pull-down resistors.

Table 2. GPIO Pin Descriptions

| Function                       | Description                                                                                                                                                                                                         |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO Selectable Control Inputs | (GPI)                                                                                                                                                                                                               |

| FINC                           | DCO frequency increment                                                                                                                                                                                             |

| FDEC                           | DCO frequency decrement                                                                                                                                                                                             |

| PLLR_FORCE_HO                  | Force holdover for RFPLL                                                                                                                                                                                            |

| PLLR_INSEL[0-2]                | Input select pins for RFPLL. There are 3 bits to select from 1 of 6 inputs.                                                                                                                                         |

| IN[0:5]_FAIL                   | Force input invalid. A low on this pin indicates to the automatic switching state machine that the associated input is not valid for selection. This is useful in applications that use their own input monitoring. |

| OE0-OE1                        | Output enable for specific outputs or group of outputs as defined by the grouping assigned in CBPro.                                                                                                                |

| SRCREQ                         | JESD204B/C SYSREF pulse request                                                                                                                                                                                     |

| OSYNC                          | Synchronizes all or a subset of output dividers identified as PPS or SYSCLK in CBPro. **Assignable to GPIO2 only.                                                                                                   |

| GPIO Selectable Status Outputs | (GPO)                                                                                                                                                                                                               |

| PLLR_LOL                       | Loss of lock for RFPLL.                                                                                                                                                                                             |

| PLLR_HO                        | This pin indicates when RFPLL has entered the holdover state.                                                                                                                                                       |

| INx_LOS                        | Loss of signal status indicator for INx.                                                                                                                                                                            |

| INx_OOF                        | Out of frequency status indicator for INx                                                                                                                                                                           |

| REF_OOF                        | Out of frequency status indicator of the reference                                                                                                                                                                  |

Table 2. GPIO Pin Descriptions (Continued)

| Function                         | Description                                                                                                              |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| REF_LOS                          | Loss of signal at XA/XB and REF pins                                                                                     |

| INTR                             | Interrupt pin for the device. Programmable Boolean combination of PLLR_LOL, INx_LOS, INx_OOF, PLLR_HO, REF_LOS, REF_OOF. |

| Primary Serial Interface (I2C/SF | 21)                                                                                                                      |

| A1/SDO                           | A1/SDO of primary SPI port. **Assignable to GPIO3 only.                                                                  |

| A0/CSb                           | A0/CSb of primary SPI port                                                                                               |

| SDA/SDIO                         | SDA/SDIO of primary SPI port                                                                                             |

| SCLK                             | SCLK of primary SPI port                                                                                                 |

#### 3.11. Device Initialization and Reset

Once power is applied and RSTb is de-asserted, the device begins loading preconfigured register values and configuration data from NVM, and performs other initialization tasks. Communicating with the device through the serial interface is possible once this initialization period is complete (see tRDY). No output clocks will be generated until the initialization is complete, and the device locks to the external (VC)XO/XTAL (see tSTART\_XO and tSTART\_XTAL). A reset, initiated using the RSTb pin or through the Device API RESTART command, restores all registers to the values stored in NVM, and all circuits, including the serial interface, will be restored to their initial state. All clocks will stop during a hard reset. Other feature-specific resets are also available. See the Si5518/12/10/08 Reference Manual and AN1360: Serial Communications and API Programming Guide for Si536x, Si540x, and Si55xx Devices for more information on different methods of resetting the device.

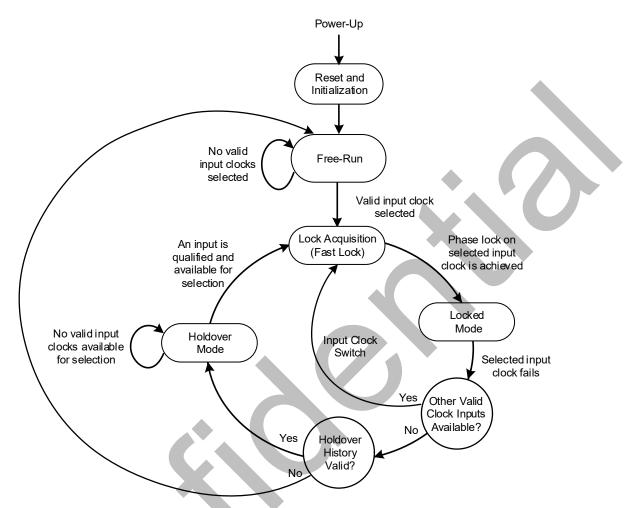

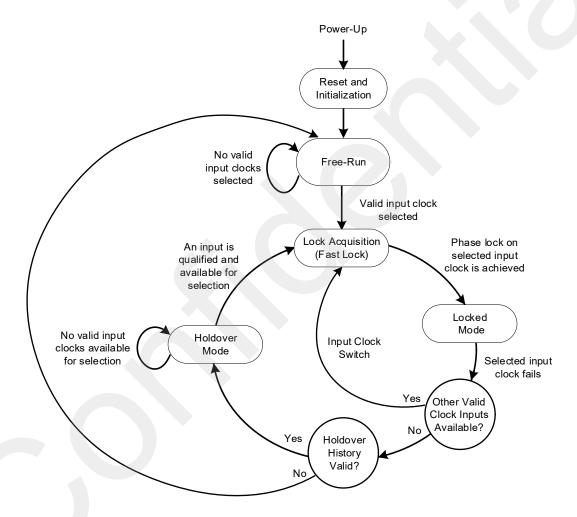

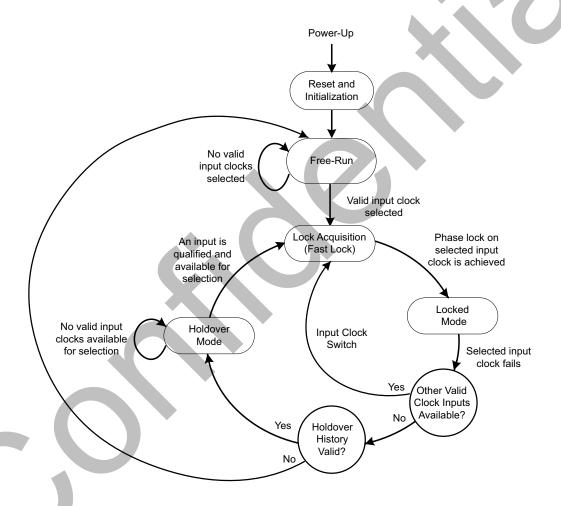

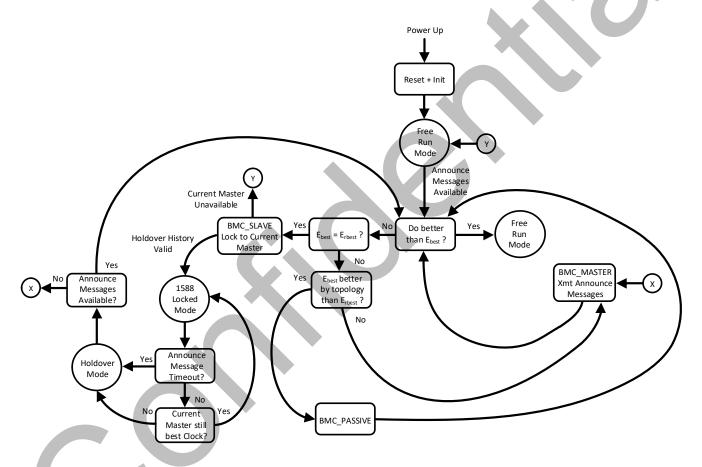

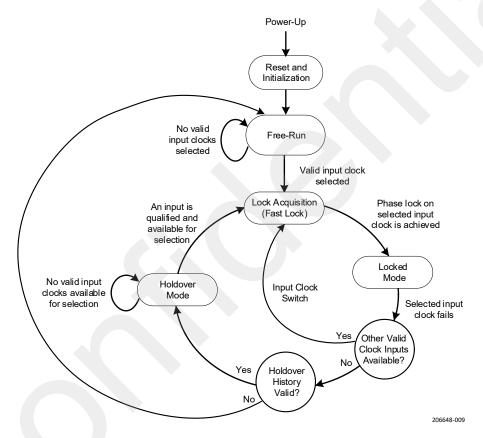

Figure 7. Modes of Operation

# 3.12. Modes of Operation

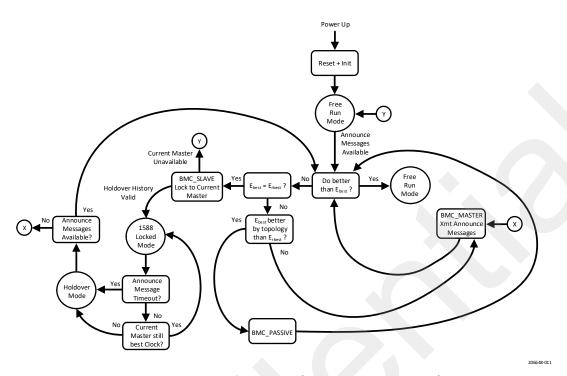

Once initialization is complete the RFPLL independently operates in one of four modes: Free-Run, Lock Acquisition, Locked, or Holdover. A state diagram showing the modes of operation is shown in the above figure. The following sections describe each of these modes in greater detail.

#### 3.12.1. Free-Run Mode

The RFPLL will automatically enter Free-Run Mode once power is applied to the device and initialization is complete. In this mode, the frequency accuracy of the generated output clocks is entirely dependent on the frequency accuracy of the reference clock source. If a XTAL is connected to the XA/XB pins, then the clock outputs will generate a frequency at the XTAL's accuracy. For example, if a XTAL is operating at -28 ppm then clock outputs will also be -28 ppm. The same is true if a XO is connected at the REF\_IN inputs instead of using XTAL at XA/XB. The frequency stability of the outputs will also be determined by the XTAL or XO.

When a TCXO or OCXO is connected to the RFPLL inputs, then the frequency accuracy and stability of the outputs will be determined by the TCXO or OCXO. This is recommended for applications that need better accuracy and stability than what the XTAL or XO can provide.

#### 3.12.2. Lock Acquisition Mode

The RFPLL independently monitors its configured inputs for a valid clock. If at least one valid clock is available for synchronization, the RFPLL will automatically start the lock acquisition process. If the fast lock feature is enabled, it will acquire lock faster than the RFPLL Loop Bandwidth would provide and then transition to the normal RFPLL loop bandwidth. During lock acquisition the outputs will generate a clock that follows the VCO frequency change as it pulls-in to the input clock frequency.

The Device API command reports the lock status of the RFPLL. When the RFPLL output frequency is within the threshold defined on the Frequency LOL (FLOL) page in CBPro, the PLL\_OUT\_OF\_FREQUENCY bit de-asserts. Some time after that, the RFPLL will pull in the remaining phase defined on the Phase LOL (PLOL) page in CBPro. Once the RFPLL is frequency and phase locked, the PLL\_LOSS\_OF\_LOCK (LOL) bit de-asserts, and the RFPLL enters locked mode.

#### 3.12.3. Locked Mode

Once locked, the RFPLL will generate clock outputs that are both frequency and phase locked to their selected input clocks. Any frequency changes (e.g., because of temperature variations) of the reference clock (REF\_IN) within the PLL loop bandwidth will be corrected by the loop ensuring 0 ppm lock to its input clock (IN). Any frequency changes of the reference clock (REF\_IN) beyond the PLL loop bandwidth will pass through to the clock output.

#### 3.12.4. Holdover Mode

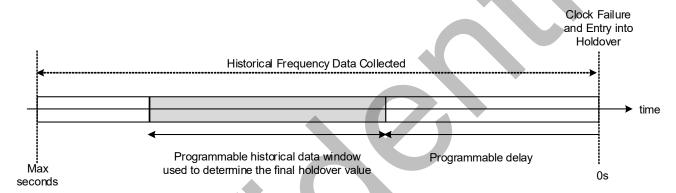

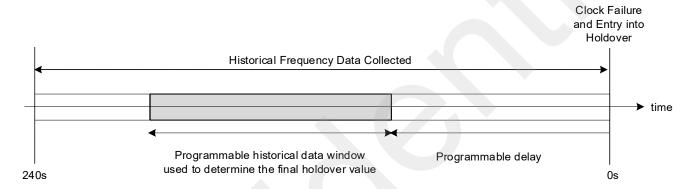

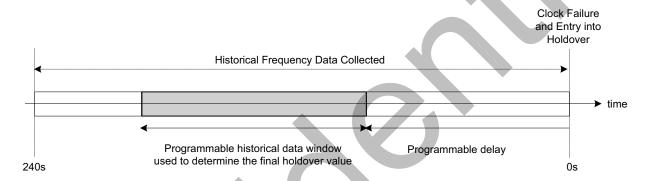

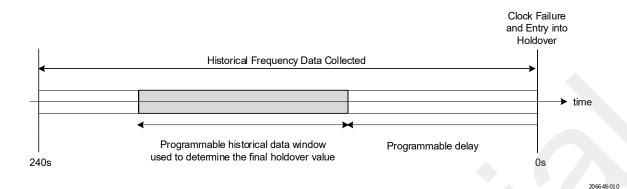

The RFPLL will automatically enter Holdover Mode when the selected input clock becomes invalid, holdover history is valid, and no other valid input clocks are available for selection. The RFPLL uses an averaged input clock frequency as its final holdover frequency to minimize the disturbance of the output clock phase and frequency when an input clock suddenly fails. The holdover circuit for the RFPLL stores historical frequency data while locked to a valid input clock. The final averaged holdover frequency value is calculated from a programmable window within the stored historical frequency data. Both the window size and delay are programmable as shown in the figure below. The window size determines the amount of holdover frequency averaging. The delay value allows ignoring frequency data that may be corrupt just before the input clock failure.

The maximum window size is a function of input frequency and is reported in CBPro the RFPLL. For higher frequency inputs up to 5000 seconds of holdover history can be stored. See CBPro for more information on this setting.

Figure 8. Programmable Holdover Window

When entering holdover, the RFPLL will pull its output clock frequency to the calculated averaged holdover frequency. While in holdover, the output frequency drift is entirely dependent on the external reference clock connected to the REF\_IN input and, if an OCXO/TCXO holdover reference is used, also dependent on the holdover reference. If the input clock becomes valid, the RFPLL will automatically exit the holdover mode and re-acquire lock to the new input clock. This process involves pulling the output clock frequency to achieve frequency and phase lock with the input clock. This pull-in process is glitchless.

The RFPLL output frequency when exiting holdover can be ramped. Just before the exit is initiated, the difference between the current holdover frequency and the new desired frequency is measured. Using the calculated difference and a user-selectable ramp rate, the output is linearly ramped to the new frequency. The RFPLL loop BW does not limit or affect ramp rate selections (and vice versa). CBPro defaults to ramped exit from holdover and free-run. The ramp rate settings are configurable for initial lock (exit from freerun), exit from holdover, and clock switching.

If ramped holdover exit is disabled, the holdover exit is governed either by (1) the RFPLL loop BW or (2) the RFPLL Fastlock bandwidth, when enabled.

#### 3.13. Status and Alarms

The Si5510/08 monitors the input clocks and reference input for status and alarms. The status and alarms provide the internal state machine with real-time phase and frequency monitoring used for making decisions, such as switching inputs or entering holdover.

#### 3.13.1. Input Clock Status

All input clocks are continuously monitored for faults using the Loss-of-Signal (LOS), Out-of-Frequency (OOF), and Phase Monitor (PHMON) alarms. When a differential input is configured as a dual CMOS input, then each CMOS input is independently monitored. Any enabled alarms for an input, such as LOS/OOF/PHMON, are logically ORed together to produce the input invalid alarm.

Any input clock with an alarm is not valid until all alarms are cleared. If RFPLL is locked to an input clock and that input clock becomes invalid, then the RFPLL may either switch to a valid input or enter holdover mode, depending on how the device is programmed.

API commands can be used to indicate if an alarm is valid, pending short term fault, under validation or invalid.

#### 3.13.1.1. Loss of Signal (LOS)

The loss of signal alarm measures the period of each input clock cycle to detect phase irregularities or missing clock edges. Each of the input LOS circuits has its own programmable sensitivity, which allows missing edges or intermittent errors to be ignored. Loss of signal sensitivity is configurable using the CBPro utility. The LOS status for each of the monitors is accessible by checking the INPUT\_STATUS API.

#### 3.13.1.2. Out of Frequency (OOF) Detection

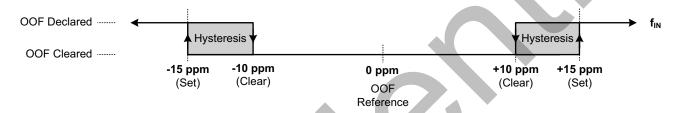

All inputs are monitored for frequency accuracy with respect to an OOF reference which is selected in Clock-Builder Pro. The OOF reference can be selected as either the XO/XTAL/VCXO or the OCXO/TCXO in dual reference mode. When available it is recommended to select the OCXO/TCXO as the OOF reference since it will have a tighter frequency accuracy compared to a free-running XTAL or a VCXO.

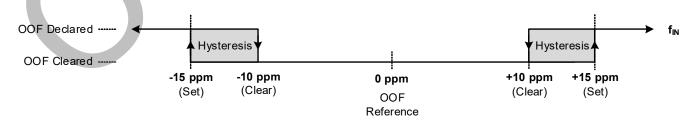

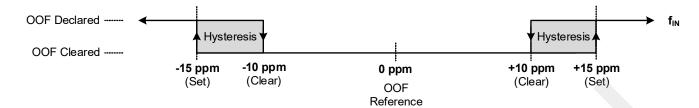

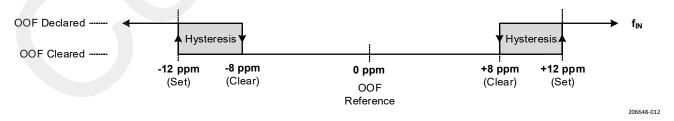

The OOF set and clear thresholds must be wider than the combined frequency accuracy of the OOF reference plus the stability of the input clock. A valid input clock frequency is one that remains within the OOF frequency range which is configurable from  $\pm 0.1$  ppm to  $\pm 500$  ppm in steps of 0.1 ppm. A configurable amount of hysteresis is also available to prevent the OOF status from toggling at the failure boundary. An example is shown in the figure below. In this case, the OOF monitor is configured with a valid frequency range of  $\pm 15$  ppm with 5 ppm of hysteresis. This OOF configuration will support a dual reference mode with a Stratum 3 level OCXO/TCXO and a SyncE input which both have  $\pm 4.6$  ppm overall frequency accuracy.

Figure 9. Example of Precise OOF Monitoring Assertion and De-assertion Triggers

#### 3.13.1.3. Phase Monitor (PHMON)

If a clock input undergoes a phase transient, a PLL locked to that input will filter the transient by its loop bandwidth; however, the transient will propagate to the output. Transients that propagate to the output have the potential to negatively impact downstream devices.

Phase Monitor (PHMON) alarm monitors the input clock phase or accumulated phase, and, if the input transient exceeds the programmable threshold, the PHMON alarm will be asserted. PHMON, like the other alarms, is quick to be asserted when the thresholds are violated yet slower to be de-asserted to prevent chattering around the threshold.

Each input clock has an independent PHMON alarm. Each alarm can be enabled/disabled individually, and its associated threshold may be independently configured. Note that OOF must be enabled and properly configured for PHMON to operate.

A ZDM input may use the PHMON alarm for monitoring purposes. However, it will have no effect on PLL bandwidth selection and will not cause input switching.

#### 3.13.1.4. Short Term Holdover

The Short-Term Holdover (STHO) feature may be used when the input clock is expected to have a short-term fault and then quickly recover.

If an input clock has STHO enabled, and an LOS/OOF/PHMON alarm is asserted, then a PLL locked to that input will enter holdover and wait for a programmable duration until all alarms on the input clock are de-asserted.

If all alarms on the input clock are de-asserted before the programmable amount of time has passed, then the PLL will gracefully relock to the same input clock. If all the alarms on the input clock are not de-asserted before the programmable amount of time has passed, then the PLL will either switch to the next priority input clock or remain in holdover, depending on the input clock selection settings.

If STHO is disabled, then the PLL will skip the short-term holdover time and immediately switch to the next priority input clock or enter holdover, depending on the input clock selection settings.

STHO may be programmed using ClockBuilder Pro to set the duration or to enable or disable the feature for each input clock individually. Note that the STHO setting will affect all PLLs assigned to that input.

#### 3.13.2. RFPLL Status

The RFPLL is continuously monitored for Loss-of-Lock (LOL). The final LOL status indicator is the logical OR of the Frequency Loss-of-Lock and Phase Loss-of-Lock statuses. See the Si5518/12/10/08 Reference Manual for more information.

#### 3.13.2.1. Loss of Lock (LOL)

There is a loss of lock (LOL) monitor for the RFPLL. The LOL monitor asserts when the RFPLL has lost synchronization with its selected input clock. Any of the GPIOs can be programmed as a dedicated loss-of-lock pin that reflects the loss-of-lock condition for the RFPLL. The LOL monitor measures both the frequency and phase difference between the input and feedback clocks of the phase detector. The frequency monitor gives frequency lock detection (FLOL) while the phase monitor indicates true phase lock PLOL by detecting one or more single slips. Both the phase and frequency LOL monitors have clear and set thresholds and a timer to prevent LOL assertion from tog-

gling or chattering as the RFPLL completes lock acquisition. The cycle slip detector also has configurable sensitivity.

#### 3.13.2.2. Frequency Loss of Lock (FLOL)

The Frequency Loss-of-Lock (FLOL) monitor measures the frequency difference between the input clock and the feedback clock. The upper and lower LOL thresholds are programmable, which dictates when the alarm will be asserted or de-asserted. It is recommended to program the clear threshold to be less than the set threshold to allow for hysteresis in the FLOL set/clear behavior. This prevents the FLOL alarm from chattering or causing multiple interrupts. FLOL, like the other alarms, is quick to be asserted when the threshold is violated yet slower to be de-asserted. The alarm validates that the frequency difference between the input and feedback clocks has truly settled to within the LOL clear threshold before the FLOL alarm is de-asserted. The time required to validate the frequency difference increases as the loop bandwidth of the PLL decreases.

#### 3.13.2.3. Lock Status Bits

There are four lock status bits that serve as four additional Frequency LOL thresholds. The Status Bit (STB) is asserted if the frequency difference between the input clock and feedback clock exceeds the programmable STB threshold. The assertion or de-assertion of an STB does not contribute to the FLOL or LOL status. The lock status bits may be read via the API. In the lock acquisition process, the de-assertion of a STB does not indicate that the PLL is frequency locked. This is because the frequency may chatter around the STB threshold. On the other hand, the de-assertion of FLOL requires the frequency difference to truly settle below the LOL clear threshold.

#### 3.13.2.4. Phase Loss of Lock (PLOL)

The Phase Loss-of-Lock (PLOL) alarm measures the phase difference between the input clock and feedback clock. The PLOL set threshold is programmable so the alarm will assert or de-assert depending on phase difference between the input and feedback clocks relative to the threshold setting. It is recommended to set the clear threshold below the set threshold to allow for hysteresis. This prevents the alarm from chattering or causing multiple interrupts. During the lock acquisition process, the input clock and feedback clock will likely have a significant frequency mismatch; so, the PLOL is not asserted until FLOL is de-asserted. Once FLOL has been de-asserted, the two frequencies are stable with respect to each other. Then the feedback clock phase can be pulled in to within the PLOL clear threshold.

## 3.13.2.5. Cycle Slip Detection

The RFPLL may be monitored for cycle slips. Like the PLOL alarm, cycle slip detection is not enabled until FLOL is de-asserted. Additionally, PLOL must be enabled for cycle slip detection to be enabled. Cycle slips both in the positive and negative direction are monitored. The API can be used to read the total count of positive cycle slips, negative cycle slips and the total count or both positive and negative slips.

#### 3.13.3. External Reference Status

An external reference must always be provided to the device. The Si5510/08 will monitor the external reference input for LOS, OOF, and LOL. If a fault is detected on the external reference, then the outputs will be disabled. Any external reference faults may be read via the API.

#### 3.13.4. Interrupt Status

The interrupt flag is asserted when any of the status indicators of the device changes state. The interrupt status may be assigned a GPIO pin, or it may be checked using an API command to show which status indicator caused the interrupt to be asserted.

The Interrupt Configuration page in CBPro lists all the status indicators that can be programmed to activate the interrupt pin.

The status indicators that are enabled are logically OR'd together so that the assertion of any of these status indicators will cause the interrupt pin to assert. The interrupt pin status depends on the sticky versions of the individual status indicators, so the interrupt pin will stay asserted until the sticky status indicators are cleared.

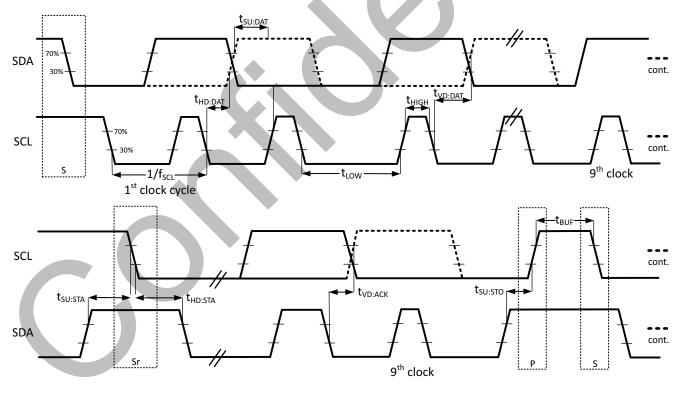

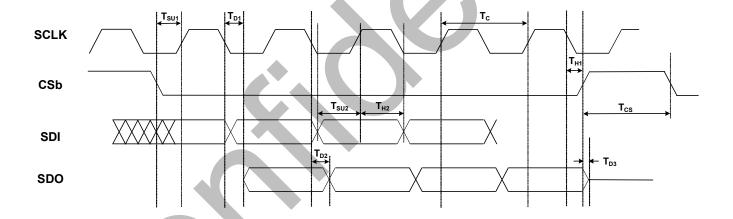

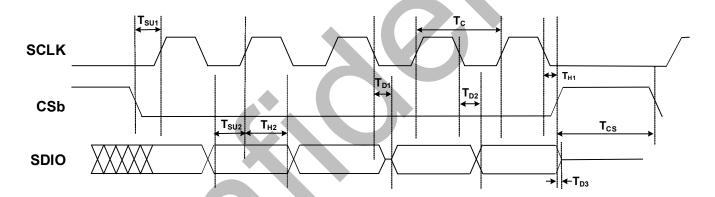

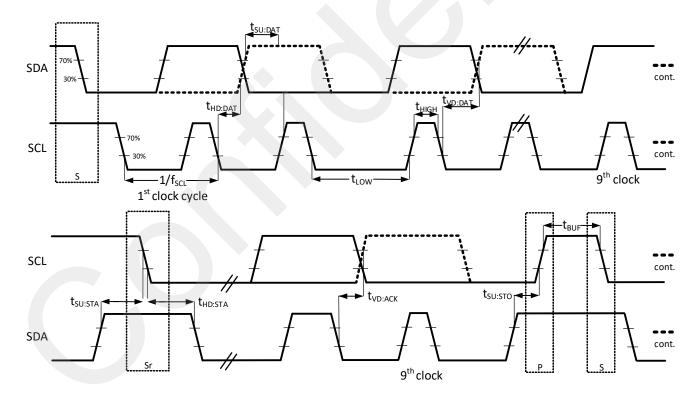

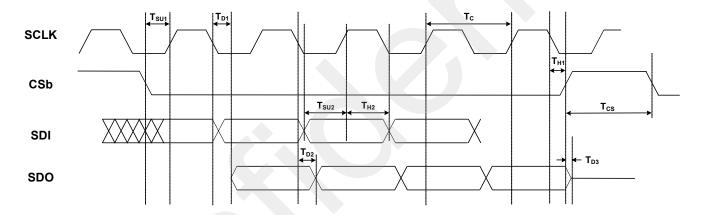

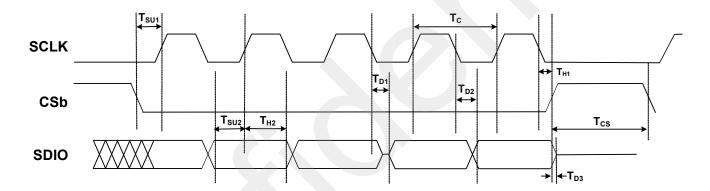

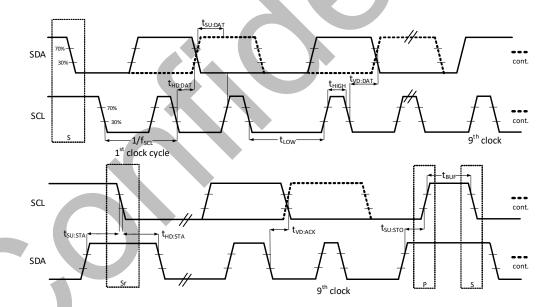

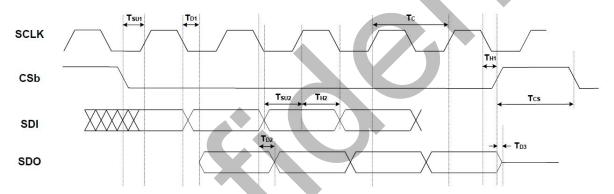

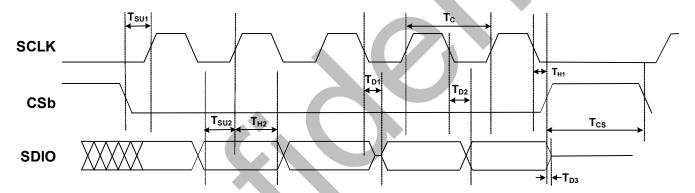

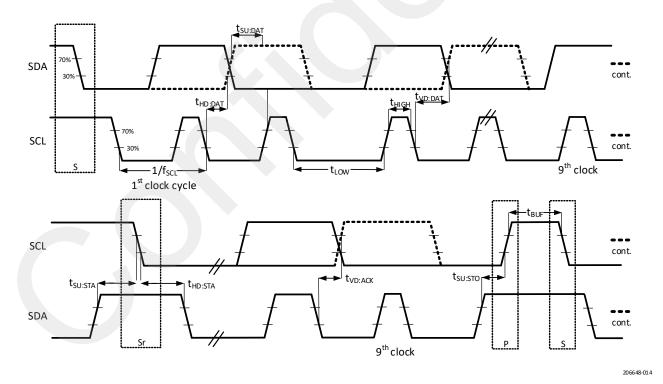

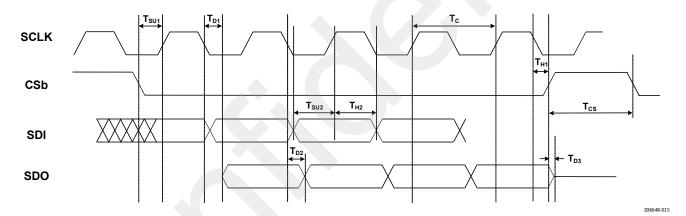

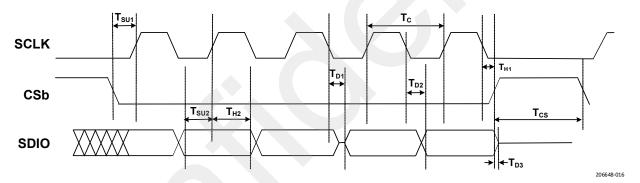

#### 3.14. Serial Interface

Configuration and operation of the Si5510/08 is controlled by reading and writing API commands using the I2C or SPI interface. The SPI mode operates in either 4-wire or 3-wire modes. The following tables define the GPIO pins assigned to the SPI interface.

| Pin Number | 3-Wire SPI | 4-Wire SPI | l <sup>2</sup> C |

|------------|------------|------------|------------------|

| 55         | CSb        | CSb        | Α0               |

| 52         | SDIO       | SDI        | SDA              |

| 53         | SCLK       | SCLK       | SCK              |

| 56         | Unused     | SDO        | A1               |

**Table 3. Primary Serial Interface Pins**

#### 3.15. NVM Programming

At power-up, the device loads its default configuration and settings from internal non-volatile memory (NVM). The NVM can be preprogrammed at the factory with a custom frequency plan such that the device starts generating clocks on its first power-up, or the NVM can be programmed in the field using the API command set. NVM programming in the field must be done with VDDA set to 3.3V. NVM programming in the field is not supported in Low-Power mode. For more details on NVM programming options, refer to Si5518/12/10/08 Reference Manual and AN1360: Serial Communications and API Programming Guide for Si536x, Si540x, and Si55xx Devices.

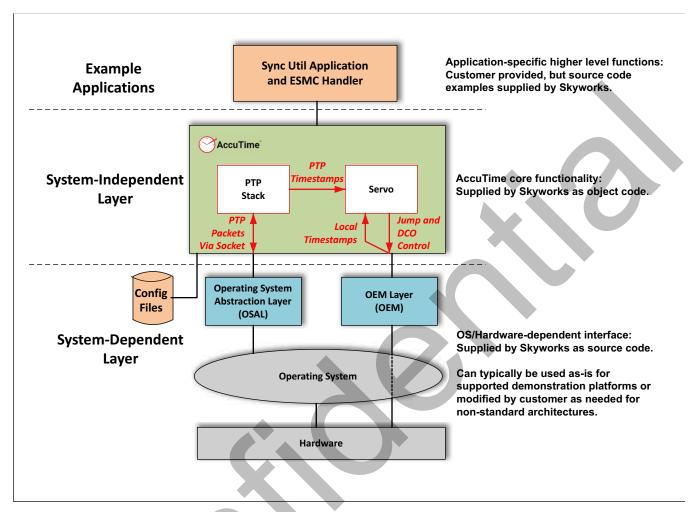

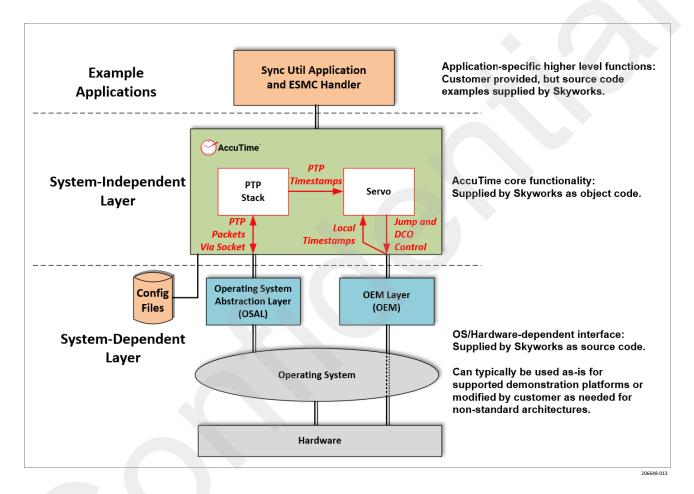

# 3.16. Application Programming Interface (API)