# ATP I-Temp NVMe pSLC PCIe Gen3 M.2 2280 SSD (HW PLP)

## N750Pi

Datasheet

Version 1.0

PLP P/N AF40GSAJA-8BAIP AF80GSAJA-8BAIP AF160GSAJA-8BBIP AF320GSAJA-8BBIP

## ATP I-Temp pSLC NVMe M.2 2280 SSD

## **Product Specification**

- Capacities:

- 40GB, 80GB, 160GB, 320GB

- Form Factors:

- M.2 2280-D2-M

- Thickness:

- Up to 3.5mm

- Weight:

- <10 grams

- PCIe Gen3 x4 performance

- Sequential Read: Up to 3,150 MB/s

- Sequential Write: Up to 2,670 MB/s:

- Read and Write IOPS (QD32)

- Random 4K Reads: Up to 147,789 IOPS

- Random 4K Writes: Up to 114,227 IOPS

- LDPC (Low Density Parity Check) ECC algorithm

- End-to-End Data Path Protection

- Compliant with PCI Express Specification Rev.3.1a

- Compliant with PCle M.2 Specification V1.1

- Compliant with NVMe Express Specification Rev.1.3b

- Support

- SMART command set support

- TRIM command

- Global wear-leveling

- Thermal throttling mechanism

- Power

- 3.3V Input Power

- Temperature

- Operating: -40°C to 85°C

- Non-Operating: -40°C to 85°C

- Reliability

- MTBF (Mean Time Between Failure):

2,000,000 hours

- Shock (Non-operating): Half Sine 1,500G

/0.5ms

- Vibration (Non-operating): Sine 16.4G

/10~2000Hz

- Data Retention (@30°C): 5 Years (with 10% P/E cycle); 1 year (with 100% P/E cycle)

- Endurance (TBW in Sequential Write)

- 40GB: 2,000 TB

- 80GB: 4,000 TB

- 160GB: 8,000 TB

- 320GB: 16,000 TB

- Certifications and Declarations

- CE

- FCC

- BSMI

- -UKCA

- Product Ecological Compliance

- RoHS

- REACH

## CONTENT

| Disc | clain | ner                                                | . 1 |

|------|-------|----------------------------------------------------|-----|

| Rev  | isior | n History                                          | . 2 |

| 1.0  | Pro   | oduct Specification                                | . 3 |

|      | 1.1   | Product Image                                      | 3   |

| _    | 1.2   | Capacity                                           | 3   |

| _    | 1.3   | Environment Specifications                         | . 4 |

| -    | 1.4   | Reliability                                        | . 4 |

| -    | 1.5   | Electrical Characteristics                         | 5   |

| _    | 1.6   | IOPS                                               | . 6 |

| -    | 1.7   | Maximum Read/Write Performance                     | . 6 |

| -    | 1.8   | Write/Erase Endurance <sup>1</sup>                 | 7   |

| 2.0  | Pro   | oduct Overview                                     | . 8 |

|      | 2.1   | Block Diagram                                      | 8   |

| 2    | 2.2   | Power Protector Data Integrity Under Power-cycling | . 8 |

| 2    | 2.3   | Auto-Refresh Technology Data Integrity Protection  | 9   |

| 3.0  | Me    | chanical Dimension & NVMe SSD Pin Assignment       | 10  |

| j    | 3.1   | Mechanical Form Factor (Units in mm)               | 10  |

| 3    | 3.2   | Pin Location                                       | 11  |

| 3    | 3.3   | Pin Assignment                                     | 11  |

| 4.0  | Coi   | mmand Set                                          | 13  |

| 4    | 4.1   | Administrative Command Set                         | 13  |

| 4    | 4.2.  | NVM Command Sets                                   | 13  |

| 4    | 4.3.  | Get Log Page                                       | 14  |

| 4    | 4.4.  | Get/Set Feature                                    | 14  |

| 4    | 4.5.  | SMART Information                                  | 15  |

| 5.0  | Pai   | rt Number Decoder                                  | 16  |

| 6.0  | Cei   | rtification and Declarations                       | 17  |

## **Disclaimer**

ATP Electronics Inc. shall not be liable for any errors or omissions that may appear in this document and disclaims responsibility for any consequences resulting from the use of the information set forth herein.

ATP may make changes to specifications and product descriptions at any time, without notice. The information in this paper is furnished for informational use only so ATP assumes no responsibility or liability for any errors or inaccuracies that may appear in this document.

All parts of the ATP documentation are protected by copyright law and all rights are reserved. This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior consent, in writing, from ATP Electronics, Inc.

Notwithstanding any clause of this Agreement, Supplier are not warranted and liable for use any Product in developing, or for incorporation into, products or services used in applications or environments requiring failsafe performance, such as in the operation of nuclear facilities, aircraft navigation or air traffic control, life support machines, surgically implanted devices, weapons systems, or other applications, devices or systems in which the failure of Product could lead directly to death, personal injury, or severe physical or environmental damage.

The information set forth in this document is considered to be "Proprietary" and "Confidential" property owned by ATP.

© Copyright ATP all rights reserved.

## **Revision History**

| Date                        | Version | Changes compared to previous issue |

|-----------------------------|---------|------------------------------------|

| Dec. 6 <sup>th</sup> , 2021 | 1.0     | - First release                    |

## **1.0 Product Specification**

## 1.1 Product Image

Figure 1-1: ATP Product Image (For Reference, PLP model)

## 1.2 Capacity

## 2 Table 1-2: Capacity Settings

| Capacity | LBA         |

|----------|-------------|

| 40GB     | 78,161,328  |

| 80GB     | 156,301,488 |

| 160GB    | 312,581,808 |

| 320GB    | 625,142,448 |

#### Note:

- 1. Sector size is 512 bytes

- 2. LBA counts are based on IDEMA (LBA1-03) standard

## 1.3 Environment Specifications

**Table 1-3-1: Environment Specification**

| Туре                 |               | Standard                 |

|----------------------|---------------|--------------------------|

| To see a creativise  | Operating     | -40°C to 85°C            |

| Temperature          | Non-Operating | -40°C to 85°C            |

| Dolotico II. maidite | Operating     | 8% to 95%, noncondensing |

| Relative Humidity    | Non-Operating | 8% to 93%, noncondensing |

| Altitude             | Operating     | 80,000 feet Max.         |

| Altitude             | Non-Operating | 80,000 feet Max.         |

| Vibration            | Non-Operating | Sine 16.4G, 10~2000Hz    |

| Shock                | Non-Operating | Half sine 1500G/0.5ms    |

Note: The environment temperature specification is based on ATP internal reliability test condition under  $+85^{\circ}\text{C}$  / $-40^{\circ}\text{C}$  of sustaining burn-in temperature.

#### 1.4 Reliability

Table1-4: Reliability

| Туре                                 | Value                                                      |

|--------------------------------------|------------------------------------------------------------|

| MTBF (@ 25°C) 1                      | >2,000,000 hours                                           |

| Data Retention (@ 30°C) <sup>2</sup> | 5 years (with 10% P/E cycle); 1 year (with 100% P/E cycle) |

#### Notes:

- 1. The Mean Time between Failures (MTBF) is calculated using a prediction methodology, Telcordia SR-332, which based on reliability data of the individual components in drive. It assumes nominal voltage, with all other parameters within specified range.

- 2. Data retention value may vary across different temperature range and is experimental result to be used for reference.

## 1.5 Electrical Characteristics

## Table 1-5-1: Supply Power

| Parameter      | Symbol | Min  | Тур. | Max  | Unit | Remark |

|----------------|--------|------|------|------|------|--------|

| Supply voltage | Vcc    | 3.15 | 3.3  | 3.45 | V    |        |

## Table 1-5-2: Power Consumption Measurement

#### **40GB**

| Parameter             | Symbol         | Min | Тур. | Max | Unit | Remark    |

|-----------------------|----------------|-----|------|-----|------|-----------|

| Sustained write power | Pw             | -   | 2.4  | 2.9 | W    | RMS value |

| Sustained read power  | P <sub>R</sub> | -   | 2.7  | 3.1 | W    | RMS value |

| Idle power            | Ps             | -   | 0.8  | 0.9 | W    | RMS value |

#### **80GB**

| Parameter             | Symbol         | Min | Тур. | Max | Unit | Remark    |

|-----------------------|----------------|-----|------|-----|------|-----------|

| Sustained write power | Pw             | -   | 2.8  | 4.2 | W    | RMS value |

| Sustained read power  | P <sub>R</sub> | -   | 2.8  | 4.7 | W    | RMS value |

| Idle power            | Ps             | -   | 0.8  | 1.7 | W    | RMS value |

#### 160GB

| Parameter             | Symbol         | Min | Тур. | Max | Unit | Remark    |

|-----------------------|----------------|-----|------|-----|------|-----------|

| Sustained write power | Pw             | -   | 3.1  | 5.2 | W    | RMS value |

| Sustained read power  | P <sub>R</sub> | -   | 3.3  | 4.6 | W    | RMS value |

| Idle power            | Ps             | -   | 0.8  | 1.7 | W    | RMS value |

#### 320GB

| Parameter             | Symbol         | Min | Тур. | Max | Unit | Remark    |

|-----------------------|----------------|-----|------|-----|------|-----------|

| Sustained write power | Pw             | -   | 3.2  | 6.8 | W    | RMS value |

| Sustained read power  | P <sub>R</sub> | -   | 2.9  | 4.8 | W    | RMS value |

| Idle power            | Ps             | -   | 0.8  | 1.7 | W    | RMS value |

#### Notes:

- ${\bf 1.} \qquad {\bf All \ power \ measured \ is \ under \ room \ temperature \ and \ using \ PCle \ interface.}$

- 2. Sequential power measured under 100% read mode or 100% write mode with 1023KB data transfers.

#### **1.6 IOPS**

**Table 1-6: IOPS (QD32) (Up to)**

| Capacity | 4K Random Read IOPS (QD32) | 4K Random Write IOPS (QD32) |

|----------|----------------------------|-----------------------------|

| 40GB     | 108,288                    | 107,776                     |

| 80GB     | 147,789                    | 111,770                     |

| 160GB    | 147,558                    | 114,227                     |

| 320GB    | 142,797                    | 110,182                     |

#### Notes:

- 1. IOPS may vary by application/system usage

- 2. IOPS is calculated by dividing capacity by (4K QD32 testing result)/4x1024

- 3. The testing is assumed under clean state and done in room temperature

#### 1.7 Maximum Read/Write Performance

Table 1-7: Performance (Up to)

| Туре                 | Capacity | Sequential Read | Sequential Write |

|----------------------|----------|-----------------|------------------|

|                      | 40GB     | 1,825 MB/s      | 570 MB/s         |

| Countral Dials Mands | 80GB     | 3,145 MB/s      | 1,155 MB/s       |

| Crystal Disk Mark    | 160GB    | 3,150 MB/s      | 2,340 MB/s       |

|                      | 320GB    | 3,145 MB/s      | 2,670 MB/s       |

#### Notes:

- 1. Performance may vary by application/system usage

- 2. Performance is measured by CrystalDiskMark in room temperature. The testing drive is assumed under clean state.

## 1.8 Write/Erase Endurance<sup>1</sup>

Table 1-8: TBW

| Capacity | Random write <sup>2</sup> | Sequential write <sup>3</sup> |

|----------|---------------------------|-------------------------------|

| 40GB     | 800 TB                    | 2,000 TB                      |

| 80GB     | 1600 TB                   | 4,000 TB                      |

| 160GB    | 3200 TB                   | 8,000 TB                      |

| 320GB    | 6400 TB                   | 16,000 TB                     |

- Endurance can be predicted based on the usage conditions applied to the device, the internal NAND component cycles, the write

amplification factor, and the wear leveling efficiency of the drive. TBW may vary depending on application, please contact ATP for TCO

evaluation if specific usage type applies.

- 2. The random endurance calculation is based on JESD219A Enterprise workload.

- 3. The sequential write endurance calculation is based on pure sequential write at 128K transfer size to run in 4K alignment test pattern

#### 2.0 Product Overview

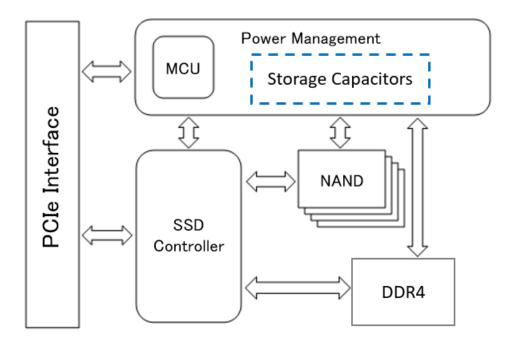

#### 2.1 Block Diagram

ATP SSD consists of below functional blocks. The advanced architecture is optimized to provide highest data reliability and transfer performance.

Figure 2-1: Block diagram for ATP NVMe SSD (PLP)

#### 2.2 Power Protector --- Data Integrity Under Power-cycling

The unstable power conditions of most applications such as transportation, networking/telecommunications and embedded systems run the risk of data loss and drive corruption during a sudden power failure.

A hardware design power protection is the ideal configuration for holding up power, ensuring a sufficient amount of reserve power during power abnormalities and minimizing the consequences of host re-designs for adding new features. During a sudden power failure, the abnormality is identified by a power loss detection circuit and activates the power protection mechanism. The device then draws power from power protection reservoir, where the reserve power is stored. The reserve power gives enough time for the flash device to conclude the last writing command without losing any data.

#### 2.3 Auto-Refresh Technology -- Data Integrity Protection

Over time the error bits accumulate to the threshold in the flash memory cell and eventually become uncorrectable despite the use of an ECC engine. In the traditional handling method, the data is moved to a different location in the flash memory; despite the corrupted data is beyond repaired before the transition.

The situation is worse in frequent read applications, such as navigation systems or OS boot-up devices. The map or operating system is preloaded into the storage media and there may be one time write and following by read operation only. Read disturbance is the result of electrical interference from multiple read operations in surrounding cells. After NAND flash accumulates 100,000 read cycles, uncorrectable ECC errors may occur in the affected pages which results in data failure in the same block.

To prevent data corruption, ATP memory product monitors the error bit levels in each read operation. When it reaches the preset threshold value, Auto-Refresh is activated by programming the data into another block before the data is corrupted. After the re-programming operation is completed, the controller reads the data and compares the data/parity to ensure data integrity.

Owing to different user experiences, please contact ATP for Auto-Refresh in real applications.

## 3.0 Mechanical Dimension & NVMe SSD Pin Assignment

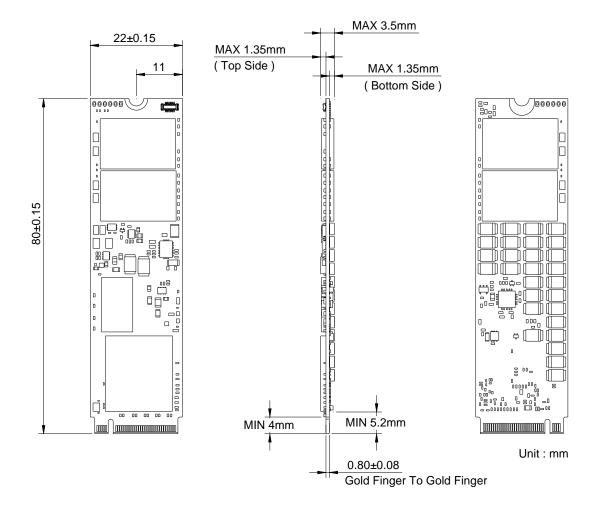

## 3.1 Mechanical Form Factor (Units in mm)

**Table 3.1: Mechanical Dimension**

| Туре          |           | Value          |

|---------------|-----------|----------------|

| M.2 2280-D2-M | Length    | 80 mm +/- 0.15 |

|               | Width     | 22 mm +/- 0.15 |

|               | Thickness | 3.5mm (MAX)    |

PLP model drawing

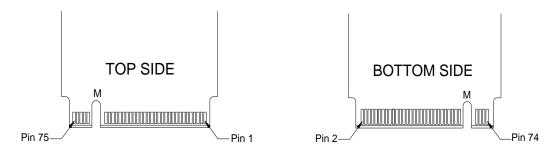

#### 3.2 Pin Location

The following figure shows the pin location of the M.2 Embedded SSD, the golden finger is with both signal and power segments.

Figure 3-2

## 3.3 Pin Assignment

Pin assignment in show in Table 3-1 below.

Table 3-1

|            | Table 5 1 |                    |            |           |              |

|------------|-----------|--------------------|------------|-----------|--------------|

| Pin<br>No. | Function  | Description        | Pin<br>No. | Function  | Description  |

| 1          | GND       | Ground             | 2          | 3.3V      | 3.3 V Source |

| 3          | GND       | Ground             | 4          | 3.3V      | 3.3 V Source |

| 5          | PETn3     | PCIe 3 Transmit(-) | 6          | N/C       | No Connect   |

| 7          | PETp3     | PCIe 3Transmit(+)  | 8          | N/C       | No Connect   |

| 9          | GND       | Ground             | 10         | LED1# (O) | LED          |

| 11         | PERn3     | PCIe 3 Receive(-)  | 12         | 3.3V      | 3.3 V Source |

| 13         | PERp3     | PCIe 3 Receive(+)  | 14         | 3.3V      | 3.3 V Source |

| 15         | GND       | Ground             | 16         | 3.3V      | 3.3 V Source |

| 17         | PETn2     | PCIe 2 Transmit(-) | 18         | 3.3V      | 3.3 V Source |

| 19         | PETp2     | PCIe 2Transmit(+)  | 20         | N/C       | No Connect   |

| 21         | GND       | Ground             | 22         | N/C       | No Connect   |

| 23         | PERn2     | PCIe 2 Receive(-)  | 24         | N/C       | No Connect   |

| 25         | PERp2     | PCIe 2 Receive(+)  | 26         | N/C       | No Connect   |

| 27         | GND       | Ground             | 28         | N/C       | Force ROM    |

| 29         | PETn1     | PCIe 1 Transmit(-) | 30         | N/C       | No Connect   |

| 31         | PETp1     | PCIe 1Transmit(+)  | 32         | N/C       | No Connect   |

| 33         | GND       | Ground             | 34         | N/C       | No Connect   |

| Pin<br>No. | Function | Description            | Pin<br>No. | Function                      | Description            |

|------------|----------|------------------------|------------|-------------------------------|------------------------|

| 35         | PERn1    | PCIe 1 Receive(-)      | 36         | N/C                           | No Connect             |

| 37         | PERp1    | PCIe 1 Receive(+)      | 38         | N/C                           | No Connect             |

| 39         | GND      | Ground                 | 40         | SMB_CLK(I/O)                  | No Connect             |

| 41         | PETn0    | PCIe 0 Transmit(-)     | 42         | SMB_DATA(I/O)                 | No Connect             |

| 43         | РЕТр0    | PCIe 0 Transmit(+)     | 44         | ALERT# (O)                    | Reserved<br>No Connect |

| 45         | GND      | Ground                 | 46         | N/C                           | No Connect             |

| 47         | PERn0    | PCIe 0 Receive(-)      | 48         | N/C                           | No Connect             |

| 49         | PERp0    | PCIe 0 Receive(+)      | 50         | PERST# (I) 3.3V               | PCIe Reset             |

| 51         | GND      | Ground                 | 52         | CLKREQ# (I/O)<br>(0/3.3V)     | Clock Request          |

| 53         | REFCLKn  | REFCLKn                | 54         | PEWAKE# (I/O)                 | Reserved               |

|            |          | (0/3.3V)               |            | No Connect                    |                        |

| 55         | REFCLKp  | REFCLKp                | 56         | Reserved for MFG_DATA         | UART_RX                |

| 57         | GND      | Ground                 | 58         | Reserved for MFG CLOCK        | UART_TX                |

| Modu       | le Key   |                        | Module Key |                               |                        |

| 67         | N/C      | No Connect             | 68         | SUSCLK(32kHz)<br>(I) (0/3.3V) | No Connect             |

| 69         | NC-PCIe  | Reserved<br>No Connect | 70         | 3.3V                          | 3.3V Source            |

| 71         | GND      | Ground                 | 72         | 3.3V                          | 3.3V Source            |

| 73         | GND      | Ground                 | 74         | 3.3V                          | 3.3V Source            |

| 75         | GND      | Ground                 |            |                               |                        |

## 4.0 Command Set

#### **4.1** Administrative Command Set

ATP NVMe SSD supports the following Administrative Command Sets:

Table 4-1

| Opcode | Optional/Mandatory | Command                     |  |

|--------|--------------------|-----------------------------|--|

| 00h    | M                  | Delete I/O Submission Queue |  |

| 01h    | M                  | Create I/O Submission Queue |  |

| 02h    | M                  | Get Log Page                |  |

| 04h    | M                  | Delete I/O Completion Queue |  |

| 05h    | M                  | Create I/O Completion Queue |  |

| 06h    | М                  | Identify                    |  |

| 08h    | M                  | Abort                       |  |

| 09h    | M                  | Set Feature                 |  |

| 0Ah    | M                  | Get Feature                 |  |

| 0Ch    | M                  | Asynchronous Event Request  |  |

| 10h    | 0                  | Firmware Commit             |  |

| 11h    | 0                  | Firmware Image Download     |  |

| 14h    | 0                  | Device Self-test            |  |

|        | NVM Command Se     | et Specific                 |  |

| 80h    | 0                  | Format NVM                  |  |

| 81h    | 0                  | Security Send               |  |

| 82h    | 0                  | Security Receive            |  |

| 84h    | 0                  | Sanitize                    |  |

### 4.2. **NVM Command Sets**

ATP NVMe SSD supports the following NVM Command Sets:

| Opcode | Optional/Mandatory | Command             |  |

|--------|--------------------|---------------------|--|

| 00h    | M                  | Flush               |  |

| 01h    | M                  | Write               |  |

| 02h    | М                  | Read                |  |

| 04h    | 0                  | Write Uncorrectable |  |

| 05h    | 0                  | Compare             |  |

| 08h    | 0                  | Write Zeros         |  |

| 09h    | 0                  | Dataset Management  |  |

## 4.3. Get Log Page

ATP NVMe SSD supports the following Get Log Page:

Table 4-3

| Opcode | Optional/Mandatory | Command                        |

|--------|--------------------|--------------------------------|

| 01h    | М                  | Error Information              |

| 02h    | М                  | SMART/Health Information       |

| 03h    | М                  | Firmware Slot Information      |

| 05h    | 0                  | Command Effects Log            |

| 06h    | 0                  | Device Self-test               |

| 07h    | 0                  | Telemetry Host-Initiated       |

| 08h    | 0                  | Telemetry Controller-Initiated |

## 4.4. Get/Set Feature

ATP NVMe SSD supports the following Get/Set Feature:

Table 4-4

| Opcode | Optional/Mandatory       | Command                            |  |

|--------|--------------------------|------------------------------------|--|

| 01h    | М                        | Arbitration                        |  |

| 02h    | М                        | Power Management                   |  |

| 03h    | 0                        | LBA Range Type                     |  |

| 04h    | М                        | Temperature Threshold              |  |

| 05h    | M                        | Error Recovery                     |  |

| 06h    | 0                        | Volatile Write Cache               |  |

| 07h    | М                        | Number of Queues                   |  |

| 08h    | М                        | Interrupt Coalescing               |  |

| 09h    | М                        | Interrupt Vector Configuration     |  |

| 0Ah    | М                        | Write Atomicity Normal             |  |

| 0Bh    | М                        | Asynchronous Event Configuration   |  |

| 0Ch    | 0                        | Autonomous Power State Transition  |  |

| 0Eh    | 0                        | Timestamp                          |  |

| 10h    | 0                        | Host Controlled Thermal Management |  |

|        | NVM Command Set Specific |                                    |  |

| 80h    | 0                        | Software Progress Marker           |  |

## 4.5. SMART Information

ATP NVMe SSD supports S.M.A.R.T. Attributes.

Table 4-5

| ID | Byte    | Bytes | Attribute Name                                    |  |

|----|---------|-------|---------------------------------------------------|--|

|    | Address |       |                                                   |  |

| 1  | 0       | 1     | Critical Warning                                  |  |

| 2  | 1~2     | 2     | Composite Temperature                             |  |

| 3  | 3       | 1     | Available Spare                                   |  |

| 4  | 4       | 1     | Available Spare Threshold                         |  |

| 5  | 5       | 1     | Percentage Used                                   |  |

| 6  | 32~47   | 16    | Data Units Read                                   |  |

| 7  | 48~63   | 16    | Data Units Written                                |  |

| 8  | 64~79   | 16    | Host Read Commands                                |  |

| 9  | 80~95   | 16    | Host Write Commands                               |  |

| 10 | 96~111  | 16    | Controller Busy Time                              |  |

| 11 | 112~127 | 16    | Power Cycles                                      |  |

| 12 | 128~143 | 16    | Power On Hours                                    |  |

| 13 | 144~159 | 16    | Unsafe Shutdowns                                  |  |

| 14 | 160~175 | 16    | Media and Data Integrity Errors                   |  |

| 15 | 176~191 | 16    | Number of Error Information Log Entries           |  |

| 16 | 192~195 | 4     | Warning Composite Temperature Time                |  |

| 17 | 196~199 | 4     | Critical Composite Temperature Time               |  |

| 18 | 200~201 | 2     | Device Temperature                                |  |

| 19 | 202~203 | 2     | Normalized ASIC Temperature                       |  |

| 20 | 216~219 | 4     | Thermal Management Temperature 1 Transition Count |  |

| 21 | 220~223 | 4     | Thermal Management Temperature 2 Transition Count |  |

| 22 | 224~227 | 4     | Total Time For Thermal Management Temperature 1   |  |

| 23 | 228~231 | 4     | Total Time For Thermal Management Temperature 2   |  |

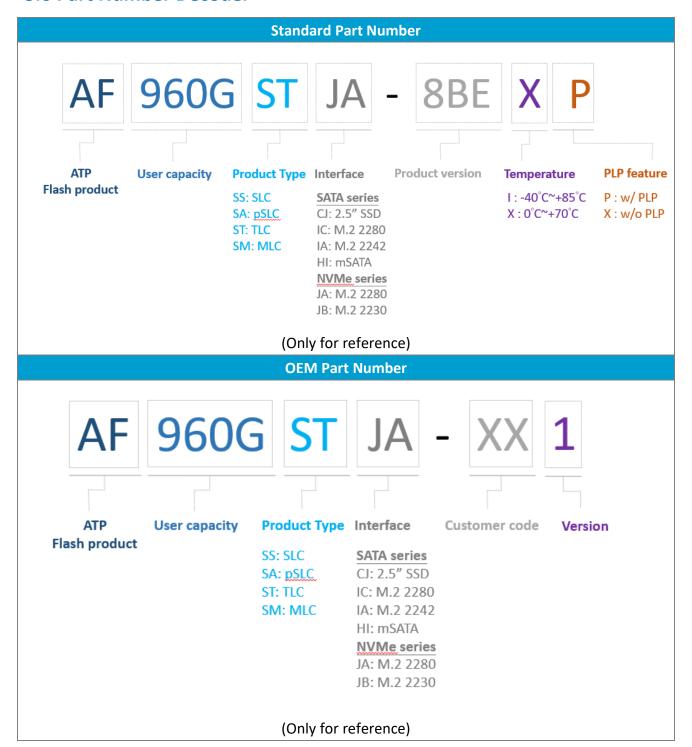

## **5.0 Part Number Decoder**

## **6.0 Certification and Declarations**

| Certification     | Mark     | Description                                                                                                                                                                                                                                                                                                                              |

|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE compliant      | ( )      | The CE marking (also known as CE mark) is a mandatory conformance mark on many products placed on the single market in the European Economic Area (EEA). The CE marking certifies that a product has met EU consumer safety, health or environmental requirements. CE stands for Conformité Européenne, "European conformity" in French. |

| FCC               | F©       | FCC Part 15 Class B was used for Evolution of United States (US) Emission Standards for Commercial Electronic Products, The United States (US) covers all types of unintentional radiators under Subparts A and B (Sections 15.1 through 15.199) of FCC 47 CFR Part 15, usually called just FCC Part 15                                  |

| BSMI<br>compliant | $\Theta$ | BSMI logo signifies the product is compliant with Taiwan EMC standard for CNS13438.                                                                                                                                                                                                                                                      |

| UKCA              | UK<br>CA | The UKCA (UK Conformity Assessed) marking is a new UK product mark for the products that conforms to the CE marking and sold in Great Britain, which is effective from 1st of January 2021.                                                                                                                                              |

| RoHS              | -        | Compliant with the Restriction of Hazardous Substances (RoHS) Directive (2011/65/EU)                                                                                                                                                                                                                                                     |

| REACH             | -        | Compliant with REACH (Registration, Evaluation, Authorization and Restriction of Chemicals which is an EU Regulation that came into force on 1 June 2007                                                                                                                                                                                 |

www.atpinc.com

TEL: +86-21-5080-2220 FAX: +86-21-9687-0000-026 sales@cn.atpinc.com